8 – location override, 9 – averaging, Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 53

DS4830A User’s Guide

53

10 11

1

2

3

4

5

6

7

8

9

18

16

15

14

13

12

28 29

19 20 21 22 23 24 25 26 27

17

30

...

1

19 20

ADACQ

SAMPLE 1

HOLD AND CONVERT SAMPLE 1 SAMPLE 2

HOLD AND CONVERT SAMPLE 2

ADC

STARTUP

ADC DATA

VALID

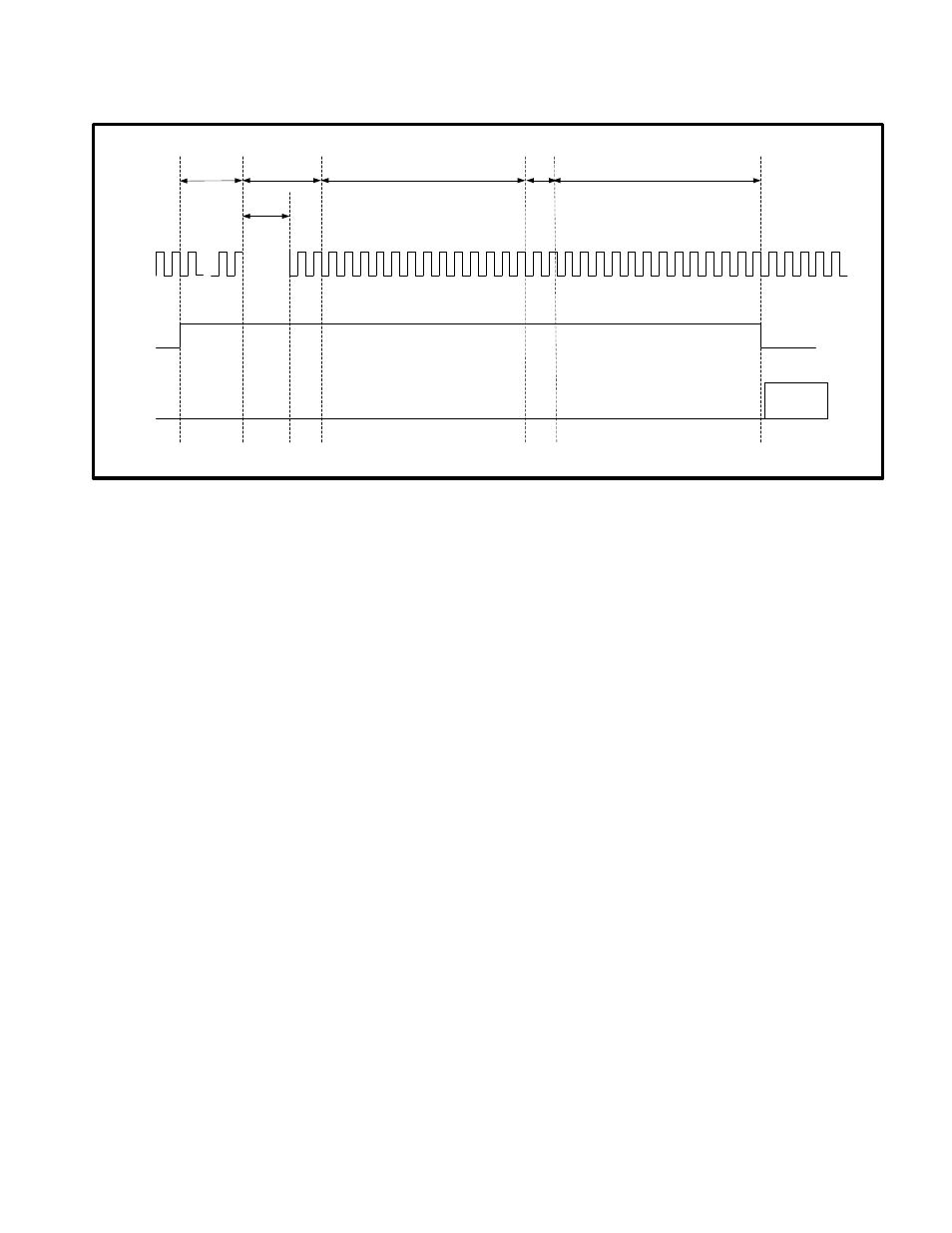

ADCCLK

ADCONV

ADDATA

Core Clock

delays

(ADACQ[3:0])

Figure 7-4: Extended Acquisition Time

7.1.8 – Location Override

By default, the ADC controller stores ADC conversion results in the ADC buffer location corresponding to the

channel number (as defined in Table 7.1). The ADC controller allows the user to override the default data buffer

location and store the ADC result at any of the buffer location (0-24). The location override is enabled by setting the

LOC_OVR bit to ‘1’ in the ADCN register. The user has to define the alternate location for storing the ADC

conversion result during ADC configuration (when ADST.ADCFG = 1). The alternate location is defined by

ADDATA[12:8] (ALT_LOC). Location override is demonstrated in Example 7.3.2,

Note: If the location override will be using the buffer locations designed for internal temperature or sample and hold,

these corresponding peripherals should be disabled (as mentioned in 7.1.1). Example, if the buffer location 22 is

used in the ADC sequence with the location override option, the internal die temperature should be disabled.

7.1. 9 – Averaging

The ADC controller supports various averaging options for each ADC channel, internal die temperature and S/Hs.

This averaging is performed automatically by the ADC controller which reduces application overheads. The ADC

controller has ADCAVG bit in the ADST register which is used to configure number of ADC samples to be averaged

for each channel. When the ADCFG bit is set to 0 and ADCAVG bit is set to ‘1’, writing to ADDATA [1:0] configures

the number of ADC samples to be averaged. User can write any value between 0-3 to select 1, 4, 8 or 16 ADC

samples averaged. See Section 7.1.2 for averaging configuration register and 7.3.3 for ADC averaging example

code.

The ADC controller has the REFAVG register to configure different averaging options for internal die temperature

and S/H. Each sample of the internal temperature is converted after the ADC sequence. See the REFAVG register

description for detailed information about averaging options for internal die temperature and sample and hold

channels.

When averaging configuration is enabled in the ADC sequence for ADC channels, internal die temperature and

S/Hs, the ADC frame sequence is changed and explained in Figure 7-5. The ADC and S/H samples are converted

back to back by the ADC controller and averaged values are reported in the data buffers. After every end of

sequence, the ADC controller converts a sample of internal die temperature.