1 – breakpoint registers, Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 167

DS4830A User’s Guide

167

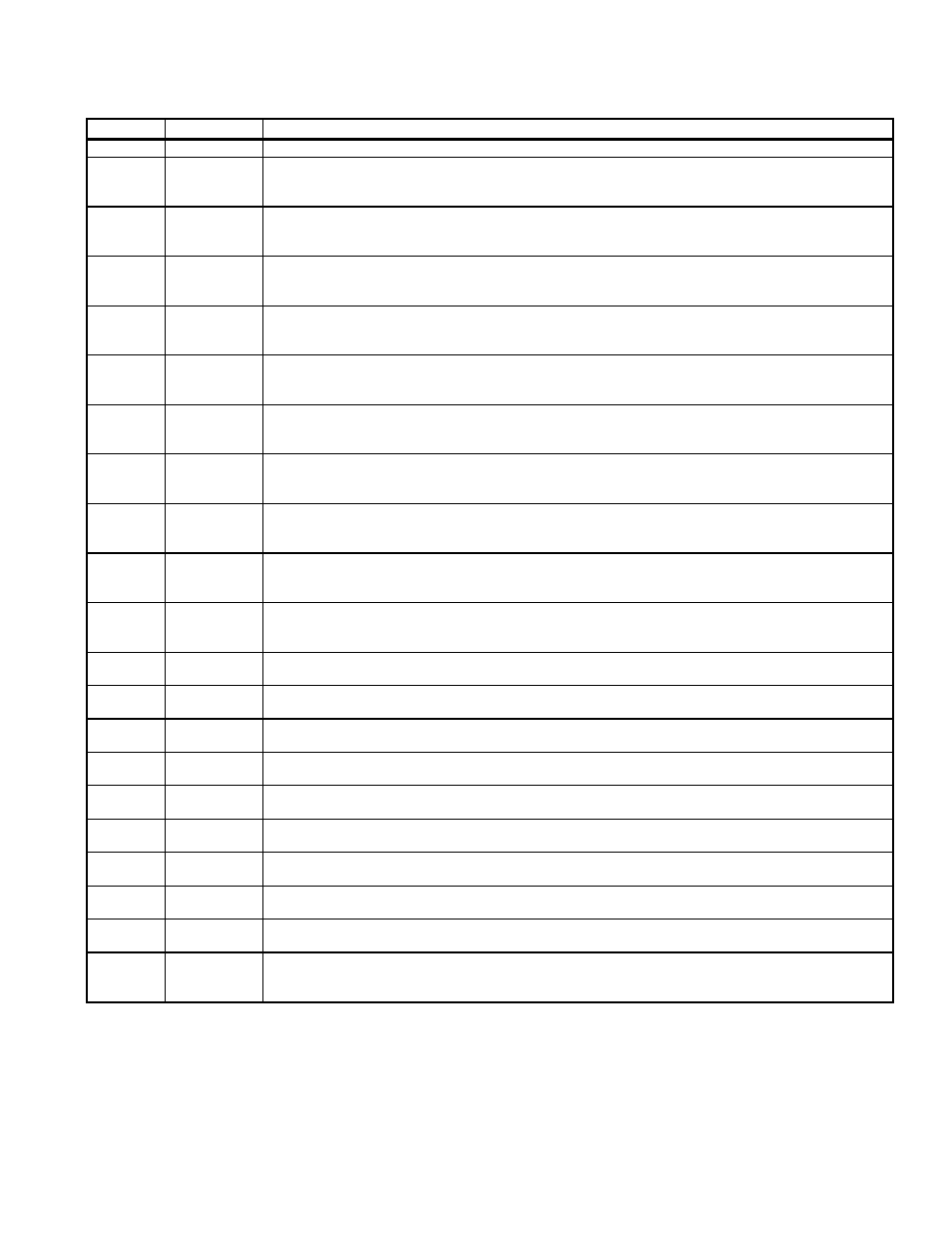

Table 21-2: Background Mode Commands

OPCODE COMMAND

OPERATION

0000-0000 No Operation No operation. (Default state for Debug Shift register).

0000-0001

Read ICDC

Read control data from the ICDC. The contents of the ICDC register will be loaded into the Debug

Shift Register via the ICDB register for host read. This command requires one follow-on transfer

cycle.

0000-0010

Read ICDF

Read flags from the ICDF. The contents of the ICDF register (one byte) will be loaded into the

Debug Shift Register via the ICDB register for host read. This command requires one follow-on

transfer cycle.

0000-0011

Read ICDA

Read data from the ICDA. The contents of the ICDA register will be loaded into the Debug Shift

Register via the ICDB register for host read. This command requires two follow-on transfer cycles

with the least significant byte first.

0000-0100

Read ICDD

Read data from the ICDD. The contents of the ICDD register will be loaded into the Debug Shift

Register via the ICDB register for host read. This command requires two follow-on transfer cycles

with the least significant byte first.

0000-0101

Read BP0

Read data from the BP0. The contents of the BP0 register will be loaded into the Debug Shift

Register via the ICDB register for host read. This command requires two follow-on transfer cycles

with the least significant byte first.

0000-0110

Read BP1

Read data from the BP1. The contents of the BP1 register will be loaded into the Debug Shift

Register via the ICDB register for host read. This command requires two follow-on transfer cycles

with the least significant byte first.

0000-0111

Read BP2

Read data from the BP2. The contents of the BP2 register will be loaded into the Debug Shift

Register via the ICDB register for host read. This command requires two follow-on transfer cycles

with the least significant byte first.

0000-1000

Read BP3

Read data from the BP3. The contents of the BP3 register will be loaded into the Debug Shift

Register via the ICDB register for host read. This command requires two follow-on transfer cycles

with the least significant byte first.

0000-1001

Read BP4

Read data from the BP4. The contents of the BP4 register will be loaded into the Debug Shift

Register via the ICDB register for host read. This command requires two follow-on transfer cycles

with the least significant byte first.

0000-1010

Read BP5

Read data from the BP5. The contents of the BP5 register will be loaded into the Debug Shift

Register via the ICDB register for host read. This command requires two follow-on transfer cycles

with the least significant byte first.

0001-0001

Write ICDC

Write control data to the ICDC. The contents of ICDB will be loaded into the ICDC register by the

debug engine at the end of the data transfer cycle.

0001-0011

Write ICDA

Write data to the ICDA. The contents of ICDB will be loaded into the ICDA register by the debug

engine at the end of the data transfer cycles. Data is transferred with the least significant byte first.

0001-0100

Write ICDD

Write data to the ICDD. The contents of ICDB will be loaded into the ICDD register by the debug

engine at the end of data transfer cycles. Data is transferred with the least significant byte first.

0001-0101

Write BP0

Write data to the BP0. The contents of ICDB will be loaded into the BP0 register by the debug

engine at the end of data transfer cycles. Data is transferred with the least significant byte first.

0001-0110

Write BP1

Write data to the BP1. The contents of ICDB will be loaded into the BP1 register by the debug

engine at the end of data transfer cycles. Data is transferred with the least significant byte first.

0001-0111

Write BP2

Write data to the BP2. The contents of ICDB will be loaded into the BP2 register by the debug

engine at the end of data transfer cycles. Data is transferred with the least significant byte first.

0001-1000

Write BP3

Write data to the BP3. The contents of ICDB will be loaded into the BP3 register by the debug

engine at the end of data transfer cycles. Data is transferred with the least significant byte first.

0001-1001

Write BP4

Write data to the BP4. The contents of ICDB will be loaded into the BP4 register by the debug

engine at the end of data transfer cycles. Data is transferred with the least significant byte first.

0001-1010

Write BP5

Write data to the BP5. The contents of ICDB will be loaded into the BP5 register by the debug

engine at the end of data transfer cycles. Data is transferred with the least significant byte first.

0001-1111

Debug

Debug command. This command forces the debug engine into debug mode and halts the CPU

operation at the completion of the current instruction after the debug command is recognized by the

debug engine.

21.1.1 – Breakpoint Registers

The DS4830A incorporates six breakpoint registers (BP0–BP5) that are configurable by the host for establishing

different types of breakpoint mechanisms. The first four breakpoint registers (BP0–BP3) are 16-bit registers that are

configurable as program memory address breakpoints. When enabled, the debug engine will force a break when a

match between the breakpoint register and the program memory execution address occurs. The final two 16-bit

breakpoint registers (BP4, BP5) are configurable in one of two possible capacities. They may be configured as data

memory address breakpoints or may be configured to support register access breakpoints. In either case, if

breakpoints are enabled and the defined breakpoint match occurs, the debug engine will generate a break condition.

The six breakpoint registers are documented below.