Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 105

DS4830A User’s Guide

105

11.2.3 – I

2

C Slave Interrupt Enable Register (I2CIE_S)

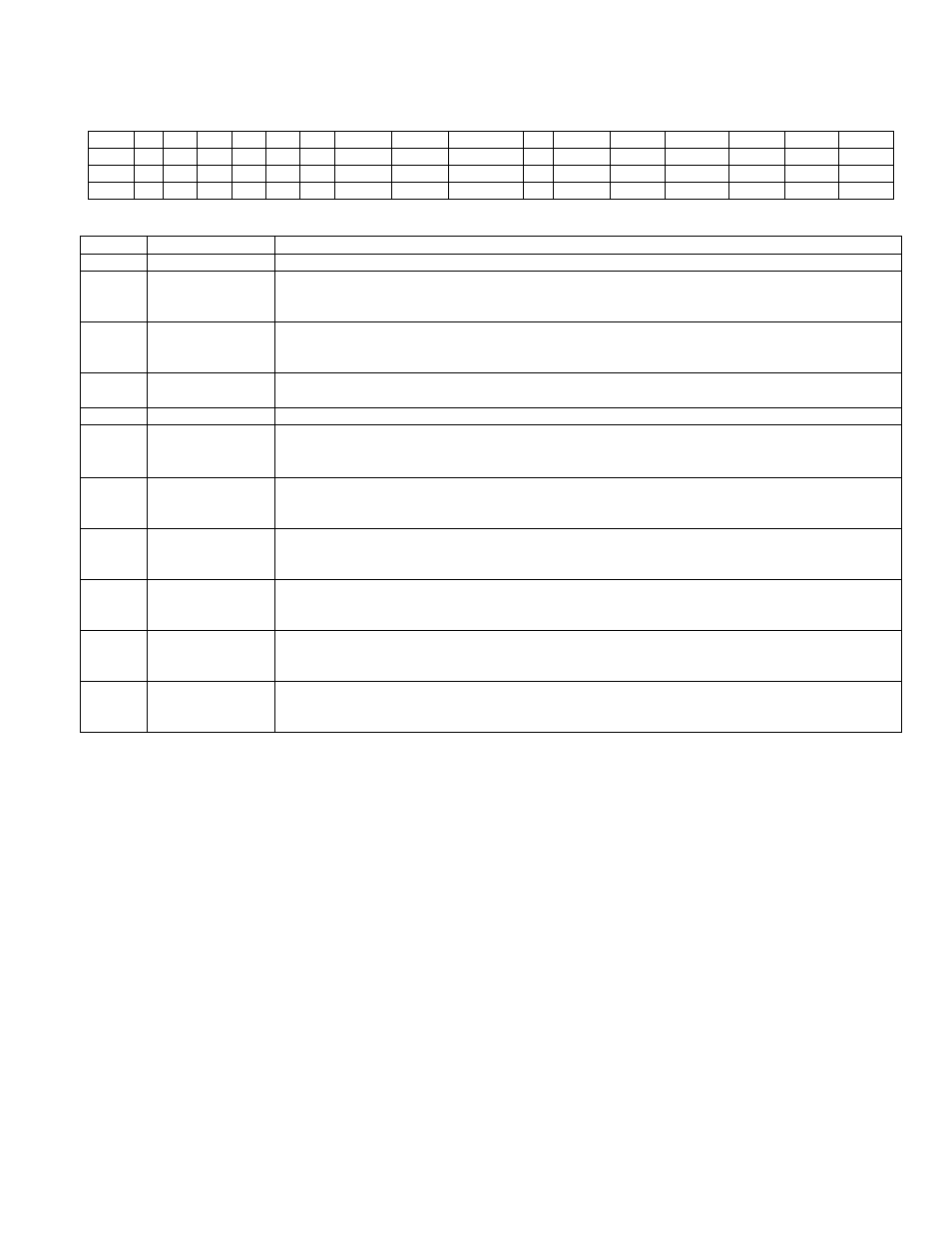

Bit

15 14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

- I2CROIE I2CGCIE I2CNACKIE - I2CAMIE I2CTOIE I2CSTRIE I2CRXIE I2CTXIE I2CSRIE

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access r

r

r

r

r

r

rw

rw

rw

r

rw

rw

rw

rw

rw

rw

BIT

NAME

DESCRIPTION

15:10

Reserved

Reserved. The user should not write to these bits.

9

I2CROIE

I

2

C

Slave Receiver Overrun Interrupt Enable. Setting this bit to ‘1’ causes an interrupt to the

CPU when a receiver overrun condition is detected (I2ROI=1). Clearing this bit to ‘0’ disables the

receiver overrun detection interrupt.

8

I2CGCIE

I

2

C

Slave General Call Interrupt Enable. Setting this bit to '1' causes an interrupt to the CPU

when a general call is detected (I2CGCI=1). Clearing this bit to '0' disables the general call

interrupt.

7

I2CNACKIE

I

2

C

Slave NACK Interrupt Enable. Setting this bit to ‘1’ causes an interrupt to the CPU when a

NACK is detected (I2CNACKI=1). Clearing this bit to ‘0’ disables the NACK detection interrupt.

6

Reserved

Reserved. The user should not write to this bit.

5

I2CAMIE

I

2

C

Slave Address Match Interrupt Enable. Setting this bit to ‘1’ causes an interrupt to the CPU

when the

I

2

C

controller detects an address that matches the I2CSLA_S value (I2CAMI=1).

Clearing this bit to ‘0’ disables the address match interrupt.

4

I2CTOIE

I

2

C

Slave Timeout Interrupt Enable. Setting this bit to ‘1’ causes an interrupt to the CPU when

an SMBUS timeout condition is detected (I2CTOI=1). Clearing this bit to ‘0’ disables the timeout

interrupt.

3

I2CSTRIE

I

2

C

Slave Clock Stretch Interrupt Enable. Setting this bit to '1' generates an interrupt to the CPU

when the clock stretch interrupt flag is set (I2CSTRI=1). Clearing this bit disables the clock stretch

interrupt.

2

I2CRXIE

I

2

C

Slave Receive Ready Interrupt Enable. Setting this bit to ‘1’ causes an interrupt to the CPU

when receive ready interrupt flag is set (I2CRXI=1). Clearing this bit to ‘0’ disables the receive

ready interrupt.

1

I2CTXIE

I

2

C

Slave Transmit Complete Interrupt Enable. Setting this bit to ‘1’ causes an interrupt to the

CPU when transmit complete interrupt flag is set (I2CTXI=1). Clearing this bit to ‘0’ disables

transmit complete interrupt.

0

I2CSRIE

I

2

C

Slave START Interrupt Enable. Setting this bit to ‘1’ causes an interrupt to the CPU when a

START condition is detected (I2CSRI=1). Clearing this bit to ‘0’ disables the START detection

interrupt.