3 – interrupt system operation, Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 43

DS4830A User’s Guide

43

enable bits and combined to create a single interrupt identification bit for that specific function. For example, the I

2

C

master has several interrupt sources; however, they all are combined to form a single identification bit, MIIR1.I2CM.

The individual register bit functions are defined as follows.

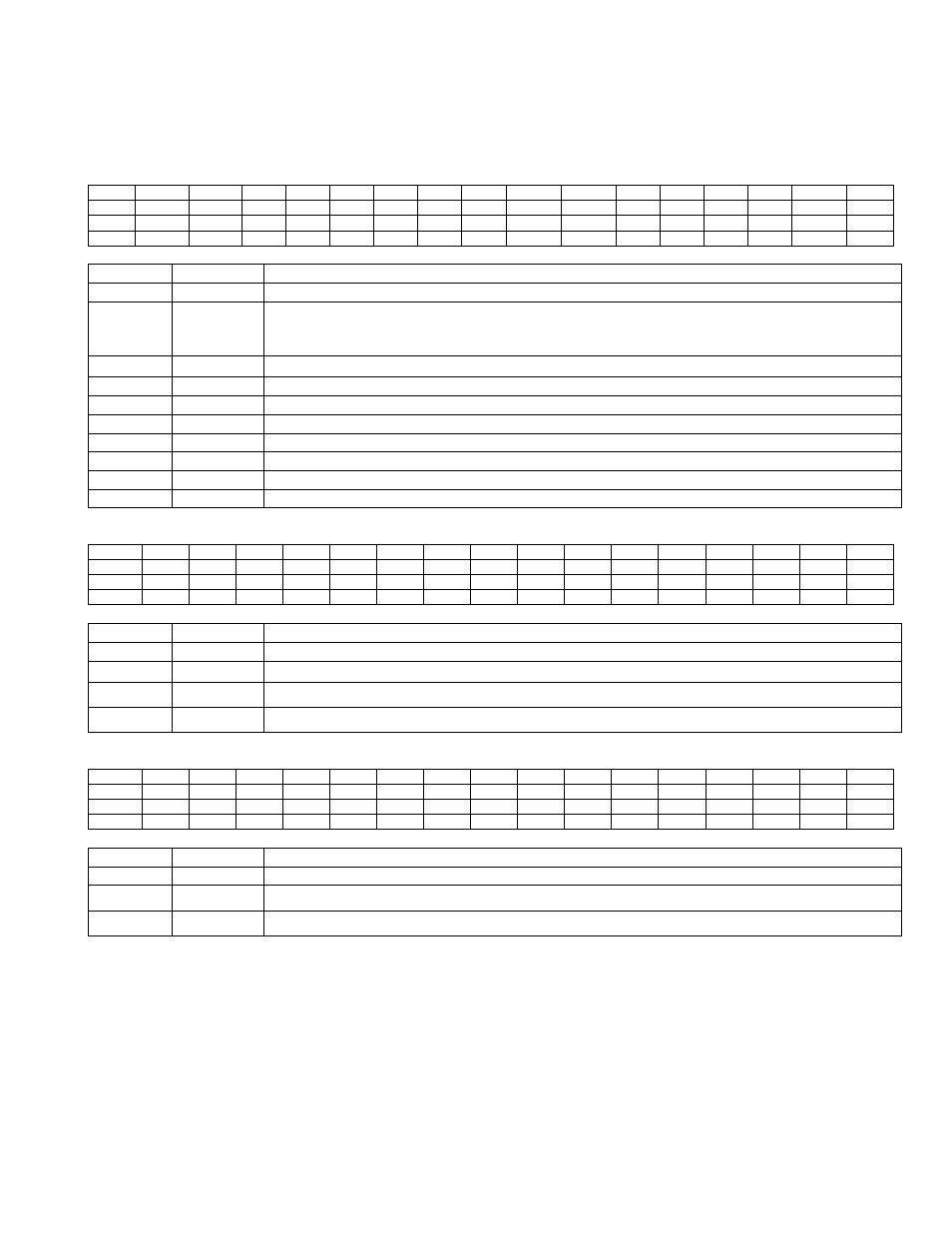

Peripheral Module 1 Interrupt Identification Register (MIIR1)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

-

-

I2CM

SVM

P6_6

P6_5 P6_4

P6_3 P6_2

P6_1

P6_0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

BIT

NAME

DESCRIPTION

15:9

Reserved

Reserved. A read returns 0.

8

I2CM

This bit is set when there is an interrupt from the I

2

C master block. The I

2

C interrupt is a

combination of all interrupts defined in the I2CST_M register for the I

2

C master block. The

Master I

2

C section has more detail on the individual interrupts.

7

SVM

This bit is set when there is an interrupt from Supply Voltage Monitor (SVM).

6

P6_6

This bit is set when there is an External GPIO Interrupt at P6.6.

5

P6_5

This bit is set when there is an External Interrupt at P6_5.

4

P6_4

This bit is set when there is an External Interrupt at P6.4.

3

P6_3

This bit is set when there is an External Interrupt at P6.3.

2

P6_2

This bit is set when there is an External Interrupt at P6.2.

1

P6_1

This bit is set when there is an External Interrupt at P6.1.

0

P6_0

This bit is set when there is an External Interrupt at P6.0.

Peripheral Module 4 Interrupt Identification Register (MIIR4)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

-

-

-

-

-

-

-

-

I2CS

TW

ADC

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

BIT

NAME

DESCRIPTION

15:3

Reserved

Reserved. A read returns 0.

2

SPI_S

This bit is set when there is an interrupt at SPI Slave.

1

TW

This bit is set when there is an interrupt from the 3Wire Block.

0

ADC

This bit is set when there is an Interrupt from the ADC.

Peripheral Module 5 Interrupt Identification Register (MIIR5)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

-

-

-

-

-

-

-

-

-

QT

SPI_M

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

BIT

NAME

DESCRIPTION

15:2

Reserved

Reserved. A read returns 0.

1

QT

This bit is set when there is an interrupt from the fast comparator

0

SPI_M

This bit is set when there is an interrupt at SPI Slave.

5.3 – Interrupt System Operation

The interrupt handler hardware responds to any interrupt event when it is enabled. An interrupt event occurs when

an interrupt flag is set. All interrupt requests are sampled at the rising edge of the clock and can be serviced by the

processor one clock cycle later, assuming the request does not hit the interrupt exception window. The one-cycle

stall between detection and acknowledgement/servicing is due to the fact that the current instruction may also be

accessing the stack. For this reason, the CPU must allow the current instruction to complete before pushing the

stack and vectoring to IV. If an interrupt exception window is generated by the currently executing instruction, the

following instruction must be executed, so the interrupt service routine will be delayed an additional cycle.

Interrupt operation in the DS4830A CPU is essentially a state machine generated long CALL instruction. When the

interrupt handler services an interrupt, it temporarily takes control of the CPU to perform the following sequence of

actions: