5 – hardware multiplier peripheral registers, Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 151

DS4830A User’s Guide

151

18.5 – Hardware Multiplier Peripheral Registers

The hardware multiplier registers are detailed below. Addresses of registers are given as “Mx[yy]” where x is the

module number (from 0 to 5 decimal) and yy is the register index (from 00h to 1Fh hexadecimal).

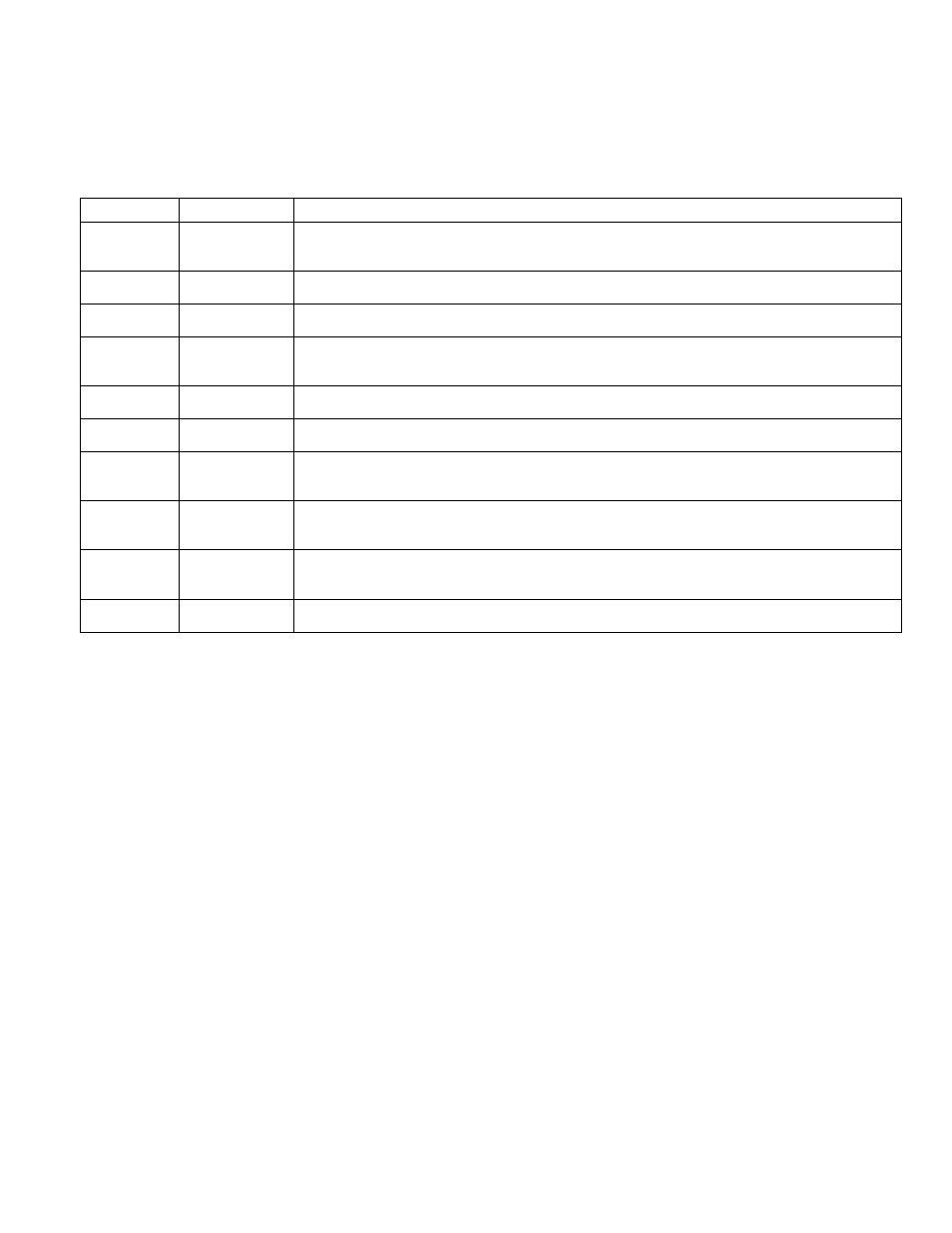

Table 18-2: Hardware Multiplier

Registers

REGISTER

ADDRESS

FUNCTION

MCNT

M3[00h]

Multiplier Control Register. Selects operation, data type, operand count, hardware square

function, and write option on the MC register. Also contains the overflow flag and the clear

control for operand registers and accumulator.

MA

M3[01h]

Multiplier Operand A Register. Used by the user software to load one of the 16-bit values for a

hardware multiplier operation.

MB

M3[02h]

Multiplier Operand B Register. Used by the user software to load one of the 16-bit values for a

hardware multiplier operation.

MC2

M3[03h]

Multiplier Accumulate Register 2. Contains the two most significant bytes of the accumulator

register. The 48-bit accumulator is formed by MC2, MC1 and MC0. The most significant bit of

this register is the signed bit for signed operations.

MC1

M3[04h]

Multiplier Accumulate Register 1. Contains bytes 3 and 2 of the accumulator register. The 48-

bit accumulator is formed by MC2, MC1 and MC0.

MC0

M3[05h]

Multiplier Accumulate Register 0. Contains the two least significant bytes of the accumulator

register. The 48-bit accumulator is formed by MC2, MC1 and MC0.

MC1R

M3[08h]

Multiplier Read Register 1. Contains bytes 1 and 0 result from the last operation when MCW bit

is 1 or the last operation is either multiply-only or multiply-negate. The contents of this register

will remain until an SFR related to the multiplier has been changed.

MC0R

M3[09h]

Multiplier Read Register 0. Contains bytes 3 and 2 result from the last operation when MCW bit

is 1 or the last operation is either multiply-only or multiply-negate. The contents of this register

will remain unchanged until an SFR related to the multiplier has been changed.

SHFT

M3[07h]

Right and Left Shift Register: The shift operations are implemented to help with fixed point

math. These operations only work on the 48-bit accumulator, MC [2:0] registers. The MCR

[1:0] registers are not affected by a shift operation.

MACSEL

M3[0Eh]

MAC Select Register. The device has internally two sets of MAC registers. Using this register

one of two MAC registers is selected which allows uninterruptible MAC operation.