Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 212

DS4830A User’s Guide

212

MOVE dst, src

Move Data

Description:

Moves data from a specified source (src) to a specified destination (dst). A list of defined

source, destination specifiers is given in the table below. Also, since src can be either 8-bit

(byte) or 16-bit (word) data, the rules governing data transfer are also explained below in the

encoding section.

Status Flags:

S, Z (if dst is Acc or AP or APC)

C, E (if dst is PSF)

Operation:

dst

src

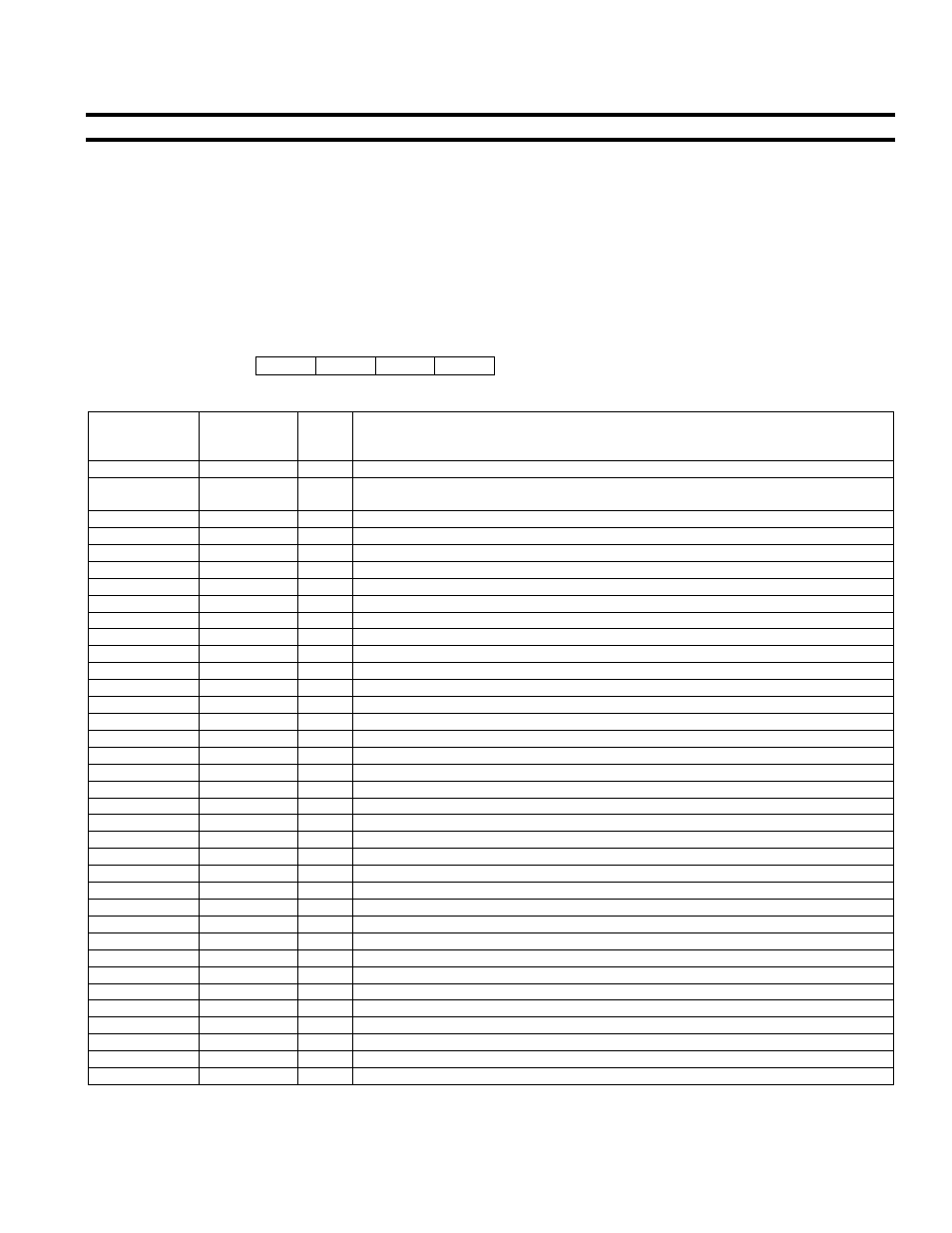

Encoding:

15

0

fddd

dddd

ssss

ssss

Source Specifier Codes

src

src Bit

Encoding

f ssss ssss

16 or

8 Bits

Description

#k

0 kkkk kkkk

8

kkkkkkkk = immediate (literal) data

MN[n]

1 nnnn

0NNN

8/16

nnnn selects one of first 16 registers in module NNN; where NNN= 0-5. Access to

2

nd

16 using PFX[n].

AP

1 0000 1000

8

Accumulator Pointer

APC

1 0001 1000

8

Accumulator Pointer Control

PSF

1 0100 1000

8

Processor Status Flag Register

IC

1 0101 1000

8

Interrupt and Control Register

IMR

1 0110 1000

8

Interrupt Mask Register

SC

1 1000 1000

8

System Control Register

IIR

1 1011 1000

8

Interrupt Identification Register

CKCN

1 1110 1000

8

Clock Control Register

WDCN

1 1111 1000

8

Watchdog Control Register

A[n]

1 nnnn 1001

16

nnnn selects one of 16 accumulators

Acc

1 0000 1010

16

Active Accumulator = A[AP]. Update AP per APC

A[AP]

1 0001 1010

16

Active Accumulator = A[AP]. No change to AP

IP

1 0000 1100

16

Instruction Pointer

@SP--

1 0000 1101

16

16-bit word @SP, post-decrement SP

SP

1 0001 1101

16

Stack Pointer

IV

1 0010 1101

16

Interrupt Vector

LC[n]

1 011n 1101

16

n selects one of 2 loop counter registers

@SPI--

1 1000 1101

16

16-bit word @SP, post-decrement SP, INS=0

@BP[Offs]

1 0000 1110

8/16

Data memory @BP[Offs]

@BP[Offs++]

1 0001 1110

8/16

Data memory @BP[Offs]; post increment OFFS

@BP[Offs--]

1 0010 1110

8/16

Data memory @BP[Offs]; post decrement OFFS

OFFS

1 0011 1110

8

Frame Pointer Offset from Base Pointer (BP)

DPC

1 0100 1110

16

Data Pointer Control Register

GR

1 0101 1110

16

General Register

GRL

1 0110 1110

8

Low byte of GR register

BP

1 0111 1110

16

Frame Pointer Base Pointer (BP)

GRS

1 1000 1110

16

Byte-swapped GR register

GRH

1 1001 1110

8

High byte of GR register

GRXL

1 1010 1110

16

Sign Extended low byte of GR register

FP

1 1011 1110

16

Frame Pointer (BP[Offs])

@DP[n]

1 0n00 1111

8/16

Data memory @DP[n]

@DP[n]++

1 0n01 1111

8/16

Data memory @DP[n], post increment DP[n]

@DP[n]--

1 0n10 1111

8/16

Data memory @DP[n], post decrement DP[n]

DP[n]

1 0n11 1111

16

n selects 1 of 2 data pointers