2 – pwm configuration register (pwmcfgn) – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 127

DS4830A User’s Guide

127

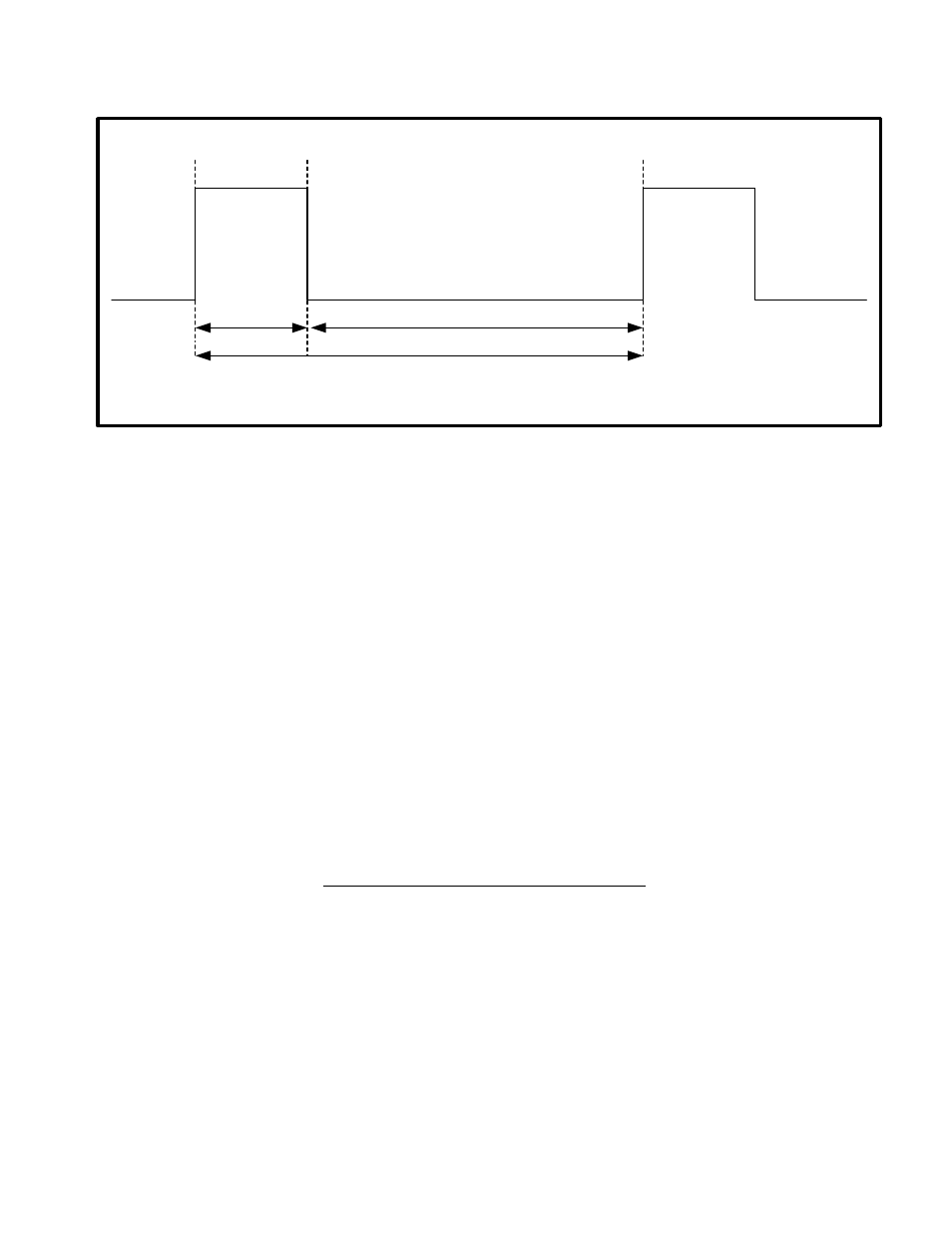

PWM Output

High Time

128 Cycles

PWM Output

Low Time

384 Cycles

PWM Frame = 512 Cycles

9-bit PWM Operation in Normal Mode

DCYCn = 128

Figure 14-4: PWM Duty Cycle Set to 128 with 9-Bit Resolution

14.2.2 – PWM Configuration Register (PWMCFGn)

This register allows independent configuration of a PWM Channel. Each PWM Channel can be independently

disabled or enabled. Each output can have from 7 to 16 bits of resolution and can be inverted.

The PWM channels 0 – 7 are multiplexed with the DAC outputs. The PWMCFGn register allows configuring the

outputs to be present at an alternate location instead of the original location.

The PWMs can be clocked using the core clock, the peripheral clock or an external clock as defined by the

PWMCFGn register.

14.2.2.1 – Pulse Spreading

The DS4830A PWMs have the ability to perform pulse spreading on the output stream. Pulse spreading divides the

PWM frame into equal slots. The DS4830A PWM controller supports nine pulse spreading options with slots varying

from 1 to 512 in the multiple of 2. For each resolution selection, up to four pulse spreading options are available.

Pulse spreading options can be selected from 2 bits in the PWMCFGn register (PS[1:0]). The PWM controller

distributes the duty cycle over the selected number of slots equally. If resolution bits are 12 and Pulse spreading

option is 3 then the PWM controller distributes the PWM Frame over 32 equal slots. By doing this, the PWM output

frequency becomes 32 times the PWM Frame frequency. In 12-bit resolution, the PWM clock period is 4096 counts

long. If Pulse spreading option is set to 3, the PWM frame is divided into 32 slots with each slot taking 128 PWM

counts. The duty cycle is equally distributed in each slot using dithering. Each slot frequency can be calculated from

the below equation and see Table 14-2 for number of slots for each resolution.

N

Slots

of

Number

Frequency

Frame

PWM

Frequency

Slot

PWM

2

×

=

, where N is resolution.