Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 133

DS4830A User’s Guide

133

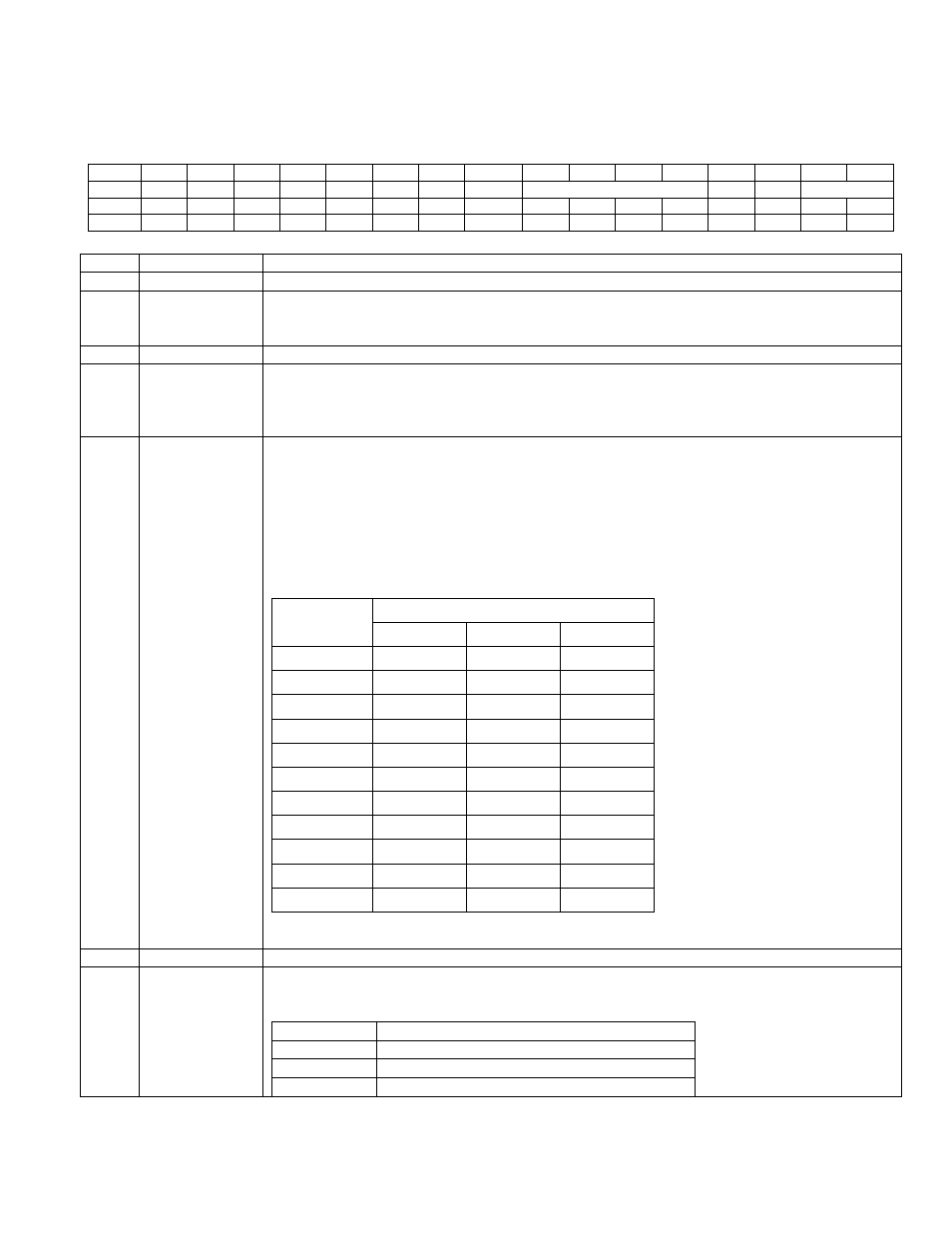

14.3.1 – PWM Control Register (PWMCN)

The PWMCN register is used to setup and start the PWM Output. To avoid undesired operation, the user should not

modify the “Reserved” bits in the PWMCN registers.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

M_EN

-

-

-

UPDATE

PWM_SEL[3:0]

-

-

REG_SEL[1:0]

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

rw

r

r

r

rw

rw

rw

rw

rw

r

r

rw

rw

BIT

NAME

DESCRIPTION

15:13

-

Reserved. The user should not write to these bits.

12

M_EN

Master Enable. This is the master enable bit for all PWM channels. All the PWM channels

will be enabled only after this bit is set to ‘1’. This bit should be set to ‘1’, after configuring

all local registers of all the required PWM channels.

11:9

-

Reserved. The user should not write to these bits.

8

UPDATE

Update. When this bit is set to ‘1’, the duty cycle of all PWM channels are updated

simultaneously. Writing a new value in the Duty Cycle register will not reflect in the PWM

output until UPDATE is set to ‘1’. Once set, this bit will automatically clear after one core

clock.

7:4

PWM_SEL[3:0] PWM Channel Select. These bits select one of the 10 PWM channels for read or write to

its local registers. These bits are used with REG_SEL[1:0] and provide access to 30 PWM

local registers (3 local registers per channel). PWM_SEL auto increments after each read

or write operation to PWMDATA register.

DCYC = Duty Cycle Register

PWMCFG = PWM Configuration Register

PWMDLY = Delay Setting Register

PWM_SEL

REG_SEL

00b

01b

1xb

0000b

DCYC0

PWMCFG0

PWMDLY0

0001b

DCYC1

PWMCFG1

PWMDLY1

0010b

DCYC2

PWMCFG2

PWMDLY2

0011b

DCYC3

PWMCFG3

PWMDLY3

0100b

DCYC4

PWMCFG4

PWMDLY4

0101b

DCYC5

PWMCFG5

PWMDLY5

0110b

DCYC6

PWMCFG6

PWMDLY6

0111b

DCYC7

PWMCFG7

PWMDLY7

1000b

DCYC8

PWMCFG8

PWMDLY8

1001b

DCYC9

PWMCFG9

PWMDLY9

>1001b

RESERVED

RESERVED

RESERVED

3:2

-

Reserved. The user should not write to these bits.

1:0

REG_SEL[1:0]

Register Select. These bits are used to select one of three local registers of the selected

PWM channel (selected by PWM_SEL[3:0] bits).

REG_SEL

Local Register Selected

00b

Duty Cycle Register (DCYCn)

01b

PWM Configuration Register (PWMCFGn)

1xb

Delay Setting Register (PWMDLYn)