Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 110

DS4830A User’s Guide

110

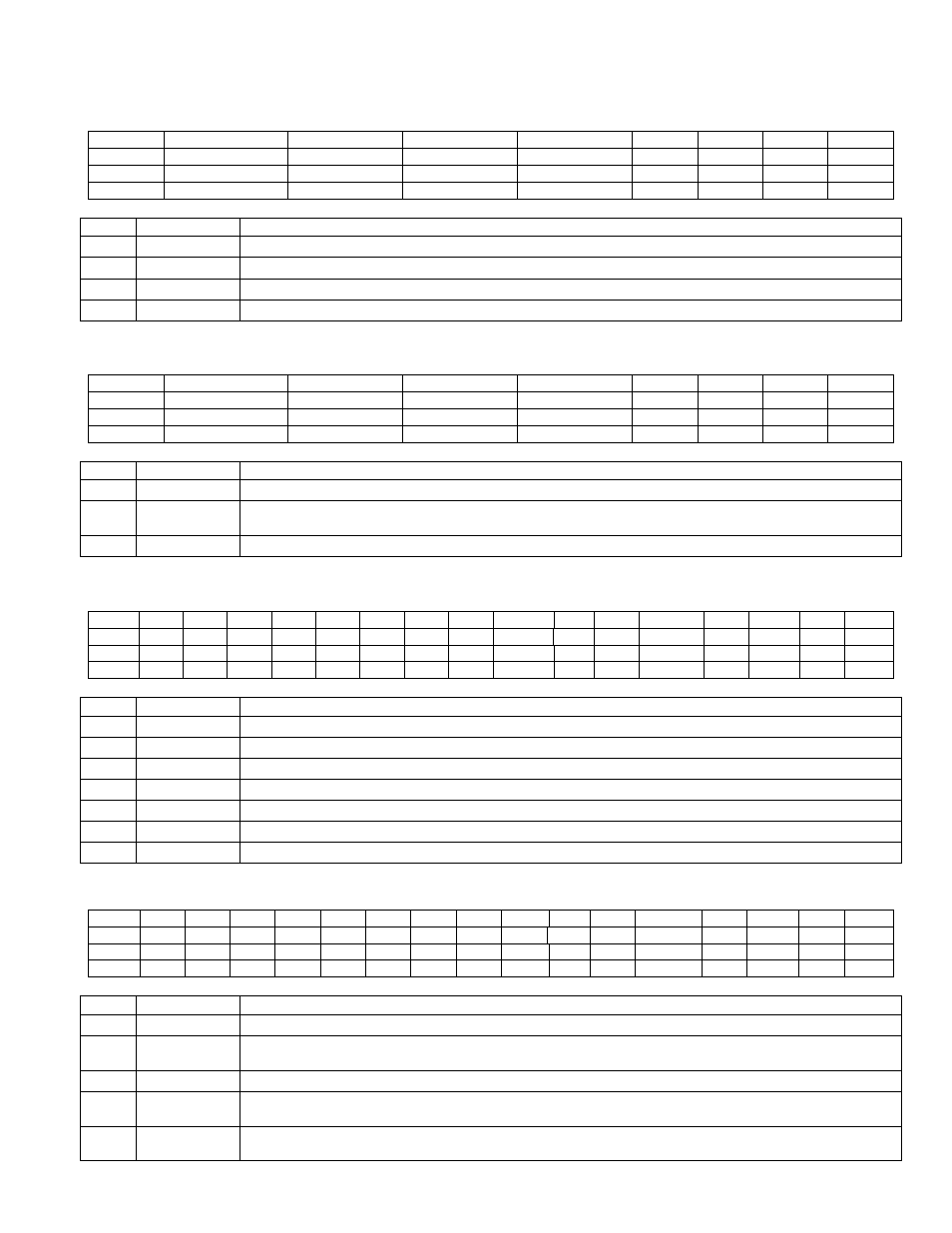

11.2.15 – I

2

C TX Page Interrupt Enable Register (I2CTXFIE)

Bit

7

6

5

4

3

2

1

0

Name

TXPG_EN

-

-

-

-

-

THSH

-

Reset

0

0

0

0

0

0

0

0

Access

rw

r

r

r

r

r

rw

r

BIT

NAME

DESCRIPTION

7

TXPG_EN

TX PAGE ENABLE: Setting this bit to ‘1’, enables the TX PAGE for all enabled slave addresses.

6:2

Reserved

Reserved. The user should not write to these bits.

1

THSH

TX Page Threshold Reach Enable: Setting this bit to ‘1’, enables TX page threshold reach interrupt.

0

Reserved

Reserved. The user should not write to this bit.

11.2.16 – I

2

C TX Page Status Register (I2CTXFST)

Bit

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

-

THSH

-

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

rw

r

BIT

NAME

DESCRIPTION

7:2

Reserved

Reserved. The user should not write to these bits.

1

THSH

TX Page Threshold Reach Enable: The

I

2

C

controller sets this bit to ‘1’ when number of bytes

remaining in the TX page is 4 for the current active slave.

0

Reserved

Reserved. The user should not write to this bit.

11.2.17 – I

2

C Receive FIFO Interrupt Enable (I2CRXFIE)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

-

-

-

FIFO_EN

-

-

-

FULL

-

THSH EMPTY

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

rw

r

r

r

rw

r

rw

rw

BIT

NAME

DESCRIPTION

15:8

Reserved

Reserved. The user should not write to these bits.

7

FIFO_EN

FIFO Enable: Setting this bit to ‘1’, enables the receive FIFO.

6:4

Reserved

Reserved. The user should not write to these bits.

3

FULL

FIFO FULL: Setting this bit to ‘1’, generates an interrupt when FIFO receives 8 bytes (FIFO FULL).

2

Reserved

Reserved. The user should not write to these bits.

1

THSH

FIFO THSH: Setting this bit to ‘1’, generates an interrupt when FIFO receives 4 bytes.

0

EMPTY

FIFO EMPTY: Setting this bit to ‘1’, generates an interrupt when receive FIFO is empty

11.2.18 – I

2

C Receive FIFO Interrupt Enable (I2CRXFST)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

-

-

-

-

-

-

-

FULL

-

THSH EMPTY

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

r

r

rw

r

rw

rw

BIT

NAME

DESCRIPTION

15:4

Reserved

Reserved. The user should not write to these bits.

3

FULL

FIFO FULL: This bit indicates that the

receive FIFO has received 8 bytes.

This bit must be cleared

to ‘0’ by software once set. Setting this bit to ‘1’ by software causes an interrupt if enabled.

2

Reserved

Reserved. The user should not write to these bits.

1

THSH

FIFO EMPTY: This bit indicates that the

receive FIFO has received 4 bytes.

This bit must be

cleared to ‘0’ by software once set. Setting this bit to ‘1’ by software causes an interrupt if enabled.

0

EMPTY

FIFO EMPTY: This bit indicates that the

receive FIFO is empty.

This bit must be cleared to ‘0’ by

software once set. Setting this bit to ‘1’ by software causes an interrupt if enabled.