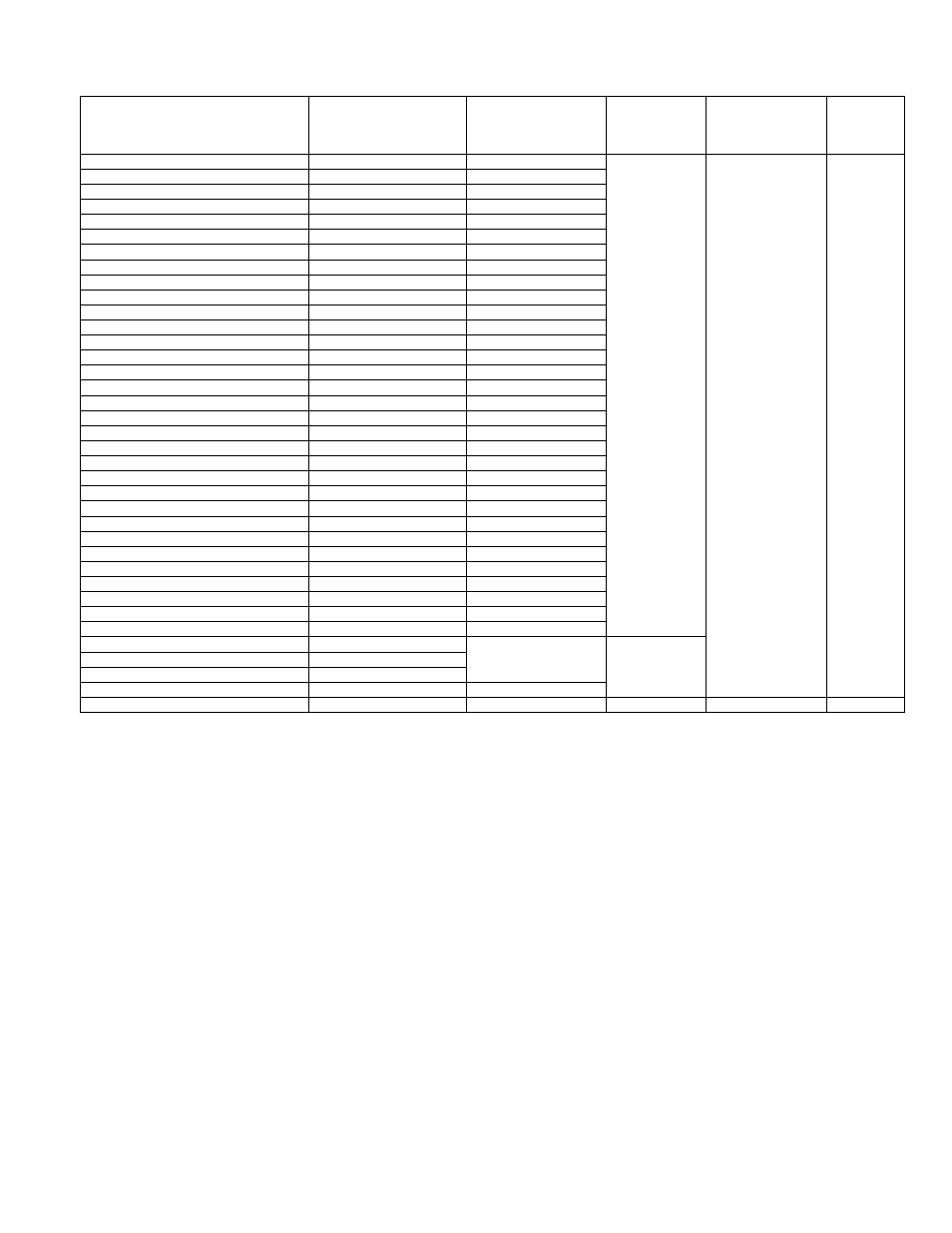

2 – module interrupt identification registers, Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 42

DS4830A User’s Guide

42

INTERRUPT

INTERRUPT FLAG

LOCAL ENABLE BIT

MODULE

INTERRUPT

IDENTIFICATI

ON BIT

INTERRUPT

IDENTIFICATION

BIT

MODULE

ENABLE

BIT

LT 0 Interrupt

LTIL.IF0

LTIL.IE0

MIIR5.QT

IIR.II5

IMR.IM5

LT 1 Interrupt

LTIL.IF1

LTIL.IE1

LT 2 Interrupt

LTIL.IF2

LTIL.IE2

LT 3 Interrupt

LTIL.IF3

LTIL.IE3

LT 4 Interrupt

LTIL.IF4

LTIL.IE4

LT 5 Interrupt

LTIL.IF5

LTIL.IE5

LT 6 Interrupt

LTIL.IF6

LTIL.IE6

LT 7 Interrupt

LTIL.IF7

LTIL.IE7

LT 8 Interrupt

LTIH.IF8

LTIH.IE8

LT 9 Interrupt

LTIH.IF9

LTIH.IE9

LT 10 Interrupt

LTIH.IF10

LTIH.IE10

LT 11 Interrupt

LTIH.IF11

LTIH.IE11

LT 12 Interrupt

LTIH.IF12

LTIH.IE12

LT 13 Interrupt

LTIH.IF13

LTIH.IE13

LT 14 Interrupt

LTIH.IF14

LTIH.IE14

LT 15 Interrupt

LTIH.IF15

LTIH.IE15

HT 0 Interrupt

HTIL.IF0

HTIL.IE0

HT 1 Interrupt

HTIL.IF1

HTIL.IE1

HT 2 Interrupt

HTIL.IF2

HTIL.IE2

HT 3 Interrupt

HTIL.IF3

HTIL.IE3

HT 4 Interrupt

HTIL.IF4

HTIL.IE4

HT 5 Interrupt

HTIL.IF5

HTIL.IE5

HT 6 Interrupt

HTIL.IF6

HTIL.IE6

HT 7 Interrupt

HTIL.IF7

HTIL.IE7

HT 8 Interrupt

HTIH.IF8

HTIH.IE8

HT 9 Interrupt

HTIH.IF9

HTIH.IE9

HT 10 Interrupt

HTIH.IF10

HTIH.IE10

HT 11 Interrupt

HTIH.IF11

HTIH.IE11

HT 12 Interrupt

HTIH.IF12

HTIH.IE12

HT 13 Interrupt

HTIH.IF13

HTIH.IE13

HT 14 Interrupt

HTIH.IF14

HTIH.IE14

HT 15 Interrupt

HTIH.IF15

HTIH.IE15

SPI Master Transfer Complete

SPICN_M.SPIC

SPICF_M.ESPII

MIIR5.SPI_M

SPI Master Write Collision

SPICN_M.WCOL

SPI Master Receive Overrun

SPICN_M.ROVR

SPI Master Mode Fault

SPICN_M.MODF

SPICN_M.MODFE

Watchdog Interrupt

WDCN.WDIF

WDCN.EWDI

N/A

IIR.IIS

IMR.IMS

When an interrupt condition occurs, its individual flag is set, even if the interrupt source is disabled at the local,

module, or global level. Interrupt flags must be cleared within the user interrupt routine to avoid repeated interrupts

from the same source. Since all interrupts vector to the address contained in the Interrupt Vector (IV) register, the

Interrupt Identification Register (IIR) may be used by the interrupt service routine to determine the module source of

an interrupt. The IIR contains a bit flag for each peripheral module and one flag associated with all system interrupts;

if the bit for a module is set, then an interrupt is pending that was initiated by that module.

In the DS4830A MIIR registers are defined for module 1, 4, and 5. In these modules the DS4830A provides two ways

to determine which block inside a module (for module 1, 4, and 5 only) caused an interrupt to occur. Module 1, 4

and 5 has Module Interrupt Identification Registers MIIR1, MIIR4 and MIIR5 respectively that indicate which of the

module’s interrupt sources has a pending interrupt. The peripheral register bits inside the module also provide a way

to differentiate among interrupt sources. Section 5.2 has more detail on the Module Interrupt Identification Registers.

The Interrupt Vector (IV) register provides the location of the interrupt service routine. It may be set to any location

within program memory. The IV register defaults to 0000h on reset or power-up, so if it is not changed to a different

address, the user program must determine whether a jump to 0000h came from a reset or interrupt source.

5.2 – Module Interrupt Identification Registers

The MIIR registers are implemented to indicate which particular function within a peripheral module has caused the

interrupt. The DS4830A has 6 peripheral modules, M0 through M5. MIIR registers are implemented in peripheral

module 1, 4 and 5. The MIIR registers are 16-bit read-only registers and all of them default to 0000h on system

reset.

Each defined bit in an MIIR register is the final interrupt from a specific function, i.e., the interrupt enable bit(s)

ANDed with the interrupt flag(s). A function can have multiple flags, but they all are ANDed with corresponding