Section 26 – miscellaneous, 1 – overview, 2 – crc8 – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 239: 1 – crc data in (crc8in), 2 – crc data out (crc8out), 3 – example, 3 – software interrupts

DS4830A User’s Guide

239

SECTION 26 – MISCELLANEOUS

26.1 – Overview

Miscellaneous features of DS4830A are

• CRC8

• Software interrupts

• General-purpose registers.

26.2 – CRC8

DS4830A has an built-in hardware CRC8. The registers used for CRC8 are CRC8IN and CRC8OUT. They are

defined in Module 1. SMBus 2.0 specification is followed for CRC algorithm (CRC polynomial is x

8

+x

2

+x+1).

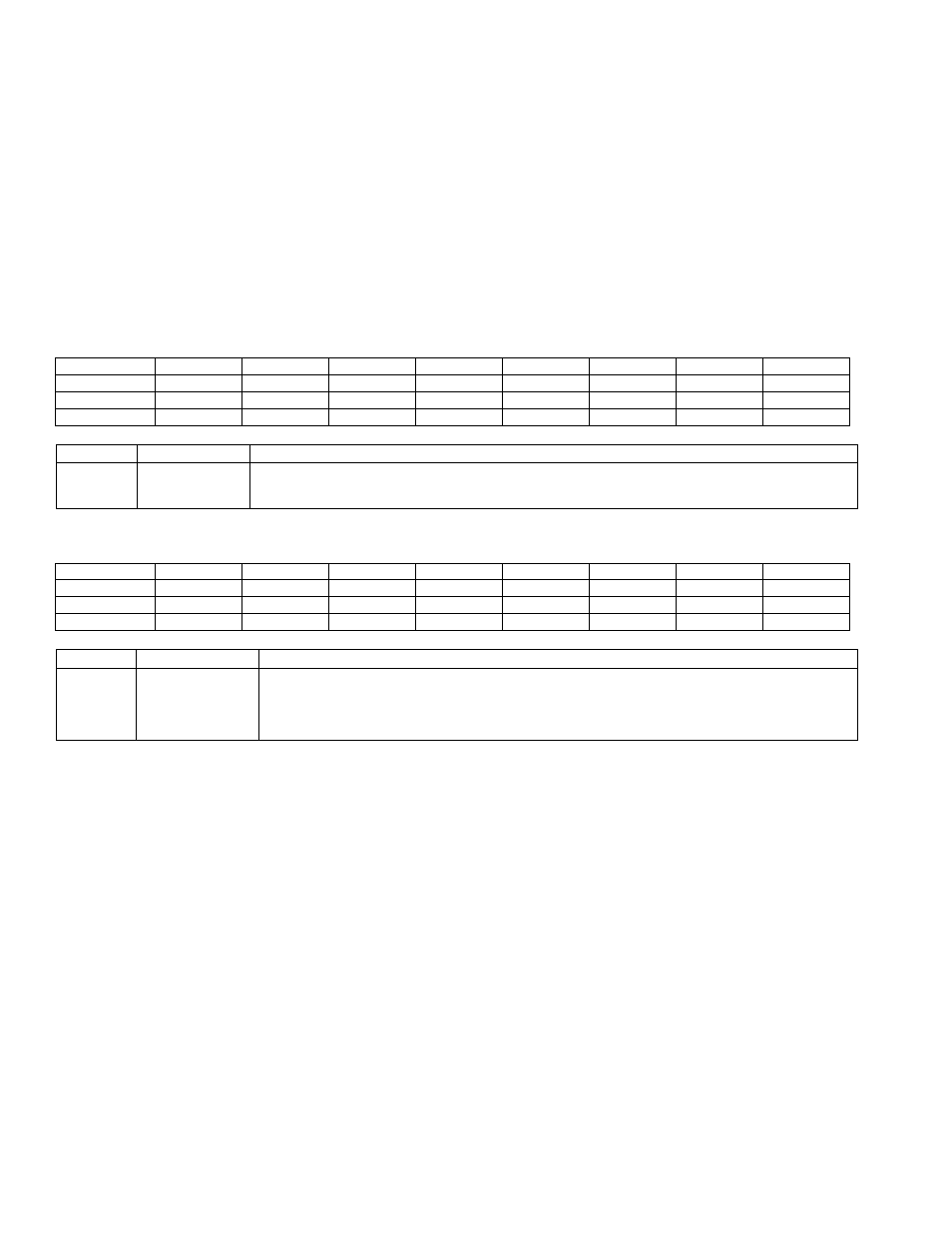

26.2.1 – CRC Data In (CRC8IN)

Bit

7

6

5

4

3

2

1

0

Name

CRC8IN_7

CRC8IN_6

CRC8IN_5

CRC8IN_4

CRC8IN_3

CRC8IN_2

CRC8IN_1

CRC8IN_0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

BIT

NAME

DESCRIPTION

7:0

CRC8IN[7:0]

CRC Data in. The user program writes data to this register for which CRC8 should be

applied to.

26.2.2 – CRC Data Out (CRC8OUT)

Bit

7

6

5

4

3

2

1

0

Name

CRC8OUT_7 CRC8OUT_6 CRC8OUT_5 CRC8OUT_4 CRC8OUT_3 CRC8OUT_2 CRC8OUT_1 CRC8OUT_0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

BIT

NAME

DESCRIPTION

7:0

CRC8OUT[7:0] CRC Data out. The user program reads CRC8 result from this register for all the

data that was written to CRC8IN.

Note: This register has to be cleared to 0x00 by software before starting a CRC8

calculation.

26.2.3 – Example

unsigned char Calculate_CRC8(unsigned char* data, int length)

{

unsigned int i = 0;

unsigned char CRC_result;

CRC8OUT = 0x00;

for( ; i

CRC8IN = data[i];

//Incrementing i in the loop takes a cycle atleast. So CRC should have been completed in this time.

}

CRC_result = CRC8OUT;

return CRC_result;

}

26.3 – Software Interrupts

The DS4830A has four software interrupts that the application program can use to generate interrupts for general-

purpose application requirements. The user can generate an interrupt by setting a bit in the USER_INT[3:0]. The

USER_INT[7:4] are single cycle read/write bits which can be used in the time critical interrupts.