2 – adc register descriptions, 1 – adc control register (adcn) – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 56

DS4830A User’s Guide

56

7.2 – ADC Register Descriptions

The ADC is controlled by the ADC SFR registers. The PINSEL register is used to configure pins as analog pins for

ADC use. Six of the registers, ADST, ADST1, ADADDR, ADCN, RPCFG, REFAVG and ADDATA are used for

setup, control, and reading from the ADC. Registers ADCG1-4 and ADVOFF which are used to adjust the gains and

offsets applied to ADC results. To avoid undesired operations, the user should not write to bits labeled as

“Reserved”.

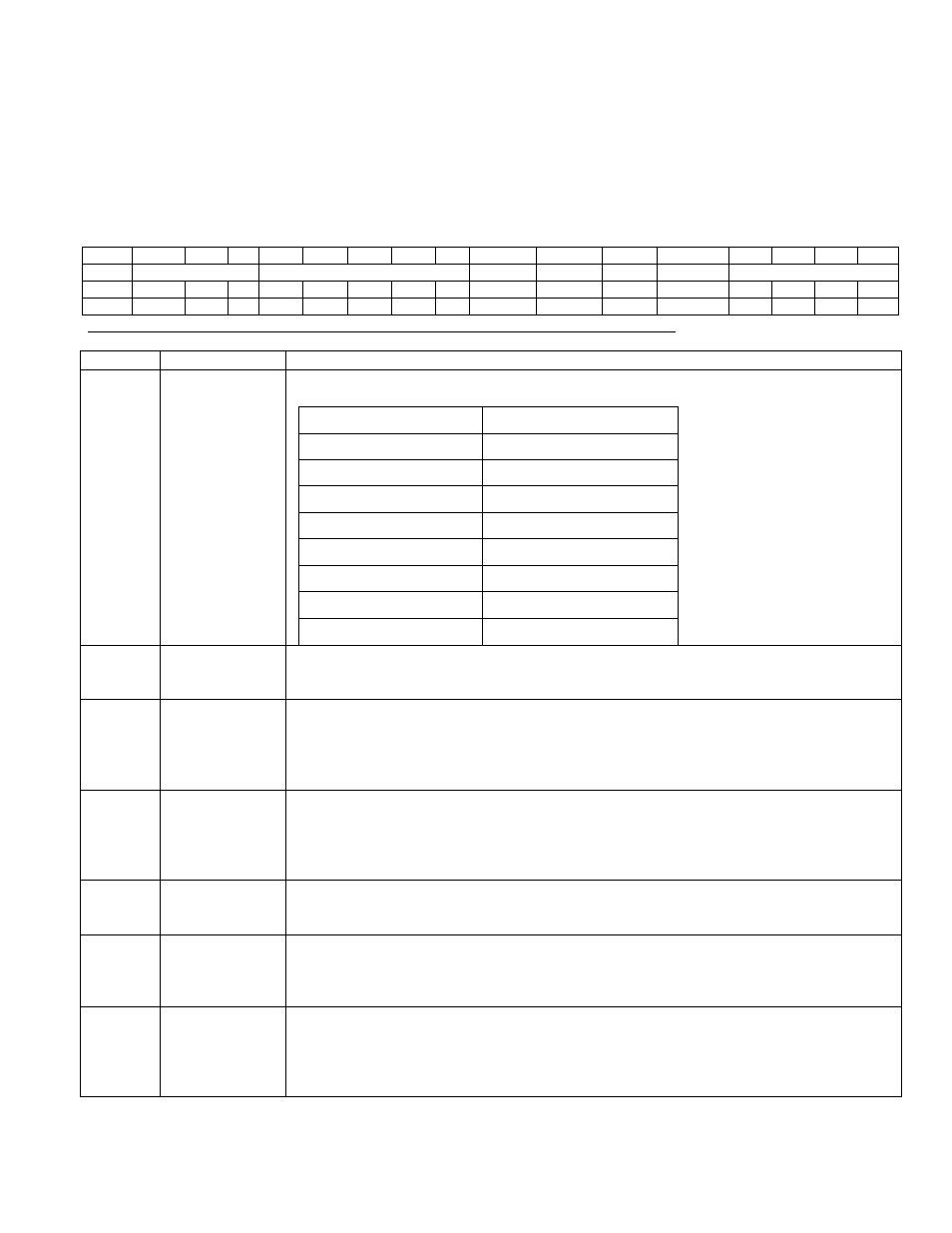

7.2.1 – ADC Control Register (ADCN)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

ADCCLK[2:0]

NUM_SMP[4:0]

ADDAINV ADCONT ADDAIE LOC_OVR

ADACQ[3:0]

Reset

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

rw*

rw* rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

* Unrestricted read, but can only be written to when ADCONV = 0 except ADDAIE bit.

BIT

NAME

DESCRIPTION

15:13

ADCCLK[2:0]

ADC Clock Divider. These bits select the ADC conversion clock in relationship to the

Core Clock.

ADCCLK[2:0]

ADC Clock

000

System Clock/8

001

System Clock/10

010

System Clock/12

011

System Clock/14

100

System Clock/16

101

System Clock/18

110

System Clock/20

111

System Clock/40

12:8

NUM_SMP[4:0] Interrupt After Number of Sample. These bits define the Number of ADC samples

required for an ADC interrupt when ADDAINV = 1. If ADDAINV is set to ‘1’, then ADC

Interrupt occurs after (NUM_SMP + 1) ADC samples and End of Sequence.

7

ADDAINV

ADC Data Available Interrupt Interval. This bit selects the condition for setting the

data available interrupt flag (ADDAI).

When ADDAINV = 0, ADDAI is set after End of Sequence.

When ADDAINV = 1, ADDAI is set after End of Sequence and after ADC Samples =

(NUM_SMP + 1).

6

ADCONT

ADC Continuous Sequence Mode. Setting this bit to ‘1’ enables the continuous

sequence mode. Clearing this bit to ‘0’ disables the continuous sequence mode. In

single sequence mode, the ADC conversion is stopped after the end of the sequence.

The user should set this bit to ‘1’, when temperature and sample and hold are also

enabled.

5

ADDAIE

ADC Data Available Interrupt Enable. Setting the ADDAIE bit to ‘1’ enables an

interrupt to be generated when the ADDAI=1. Clearing this bit to ‘0’ disables an

interrupt from generating when ADDAI=1. This bit is unconditional writable.

4

LOC_OVR

Location override bit. Setting this bit to ‘1’ enables the user to select an alternate

location for storing ADC conversion results. The alternate location is defined by

ADDATA[12:8] (ALT_LOC). By default, the ADC conversion results are stored in ADC

buffer location corresponding to channel number. See Table 7-1.

3:0

ADACQ[3:0]

ADC Acquisition Extension Bits [3:0]. These bits are used to extend sample

acquisition time if the corresponding ADC Acquisition Extension is enabled

(ADDATA.ADACQEN =1 when ADST.ADCFG is set to ‘1’). See ADC Conversion Time

Section for details. The ADC acquisition extension should not be used when the fast

comparator is used for the same channel.