2 – sample and hold register descriptions, Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 70

DS4830A User’s Guide

70

8.2 – Sample and Hold Register Descriptions

The sample and hold has two SFRs. These are Sample and Hold Control Register (SHCN) and Sample and Hold

Internal Trigger Enable register (SENR). The SHCN register controls both sample and holds. The SENR controls

the internal sample pulse for both sample and holds. The sample and hold SFRs are located in module 4.

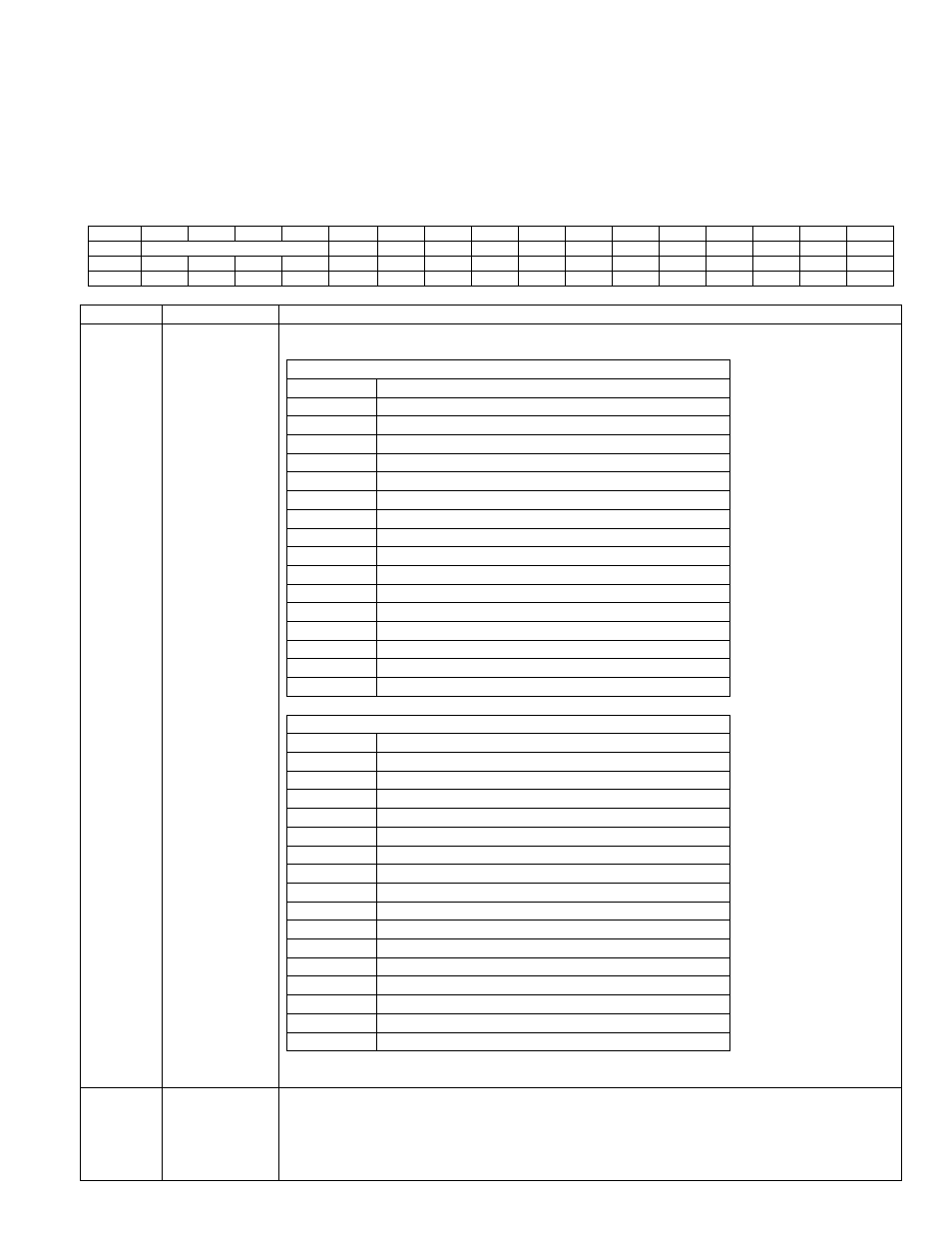

8.2.1 – Sample and Hold Control Register (SHCN)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

SSC[3:0]

FAST_MODE

PIN_DIS1 PIN_DIS0 SH_DUAL

-

SH1_ALIGN

SHDAI1_EN

SMP_HLD1

CLK_SEL

SH0_ALIGN

SHDAI0_EN

SMP_HLD0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r

rw

rw

rw

rw

rw

rw

rw

BIT

NAME

DESCRIPTION

15:12

SSC[3:0]

STOP Sample Control. These bits control the end of the sample and hold sampling

relative to the SHEN0 and SHEN1 pulse.

CLK_SEL = 0

SSC[3:0]

STOP Sampling

0000

Falling Edge of SHEN0/SHEN1

0001

Reserved

0010

Reserved

0011

Reserved

0100

300ns after rising edge of SHEN0/SHEN1

0101

350ns after rising edge of SHEN0/SHEN1

0110

450ns after rising edge of SHEN0/SHEN1

0111

550ns after rising edge of SHEN0/SHEN1

1000

750ns after rising edge of SHEN0/SHEN1

1001

1us after rising edge of SHEN0/SHEN1

1010

1.5us after rising edge of SHEN0/SHEN1

1011

1.75us after rising edge of SHEN0/SHEN1

1100

2us after rising edge of SHEN0/SHEN1

1101

2.5us after rising edge of SHEN0/SHEN1

1110

4us after rising edge of SHEN0/SHEN1

1111

5us after rising edge of SHEN0/SHEN1

CLK_SEL = 1

SSC[3:0]

STOP Sampling

0000

Falling Edge of SHEN0/SHEN1

0001

21 ext-clock after rising edge of SHEN0/SHEN1

0010

22 ext-clock after rising edge of SHEN0/SHEN1

0011

23 ext-clock after rising edge of SHEN0/SHEN1

0100

24 ext-clock after rising edge of SHEN0/SHEN1

0101

25 ext-clock after rising edge of SHEN0/SHEN1

0110

26 ext-clock after rising edge of SHEN0/SHEN1

0111

27 ext-clock after rising edge of SHEN0/SHEN1

1000

28 ext-clock after rising edge of SHEN0/SHEN1

1001

29 ext-clock after rising edge of SHEN0/SHEN1

1010

30 ext-clock after rising edge of SHEN0/SHEN1

1011

31 ext-clock after rising edge of SHEN0/SHEN1

1100

32 ext-clock after rising edge of SHEN0/SHEN1

1101

33 ext-clock after rising edge of SHEN0/SHEN1

1110

34 ext-clock after rising edge of SHEN0/SHEN1

1111

35 ext-clock after rising edge of SHEN0/SHEN1

Note: A minimum sample time of 300nSec must be used when external clock is

used to guarantee accurate results.

11

FAST_MODE

Fast Mode Enable. Setting this bit to ‘1’ enables the fast operation for Sample and Hold

0. In this mode, Sample and Hold 0 is guaranteed to get a conversion slot in the ADC

conversion sequence every 125

µs and the user can issue sample pulses at an interval

of 125

µs. During fast mode, the sample and hold conversion priority is increased over

voltage channels in the sequence and the voltage conversions will be delayed. When