Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 106

DS4830A User’s Guide

106

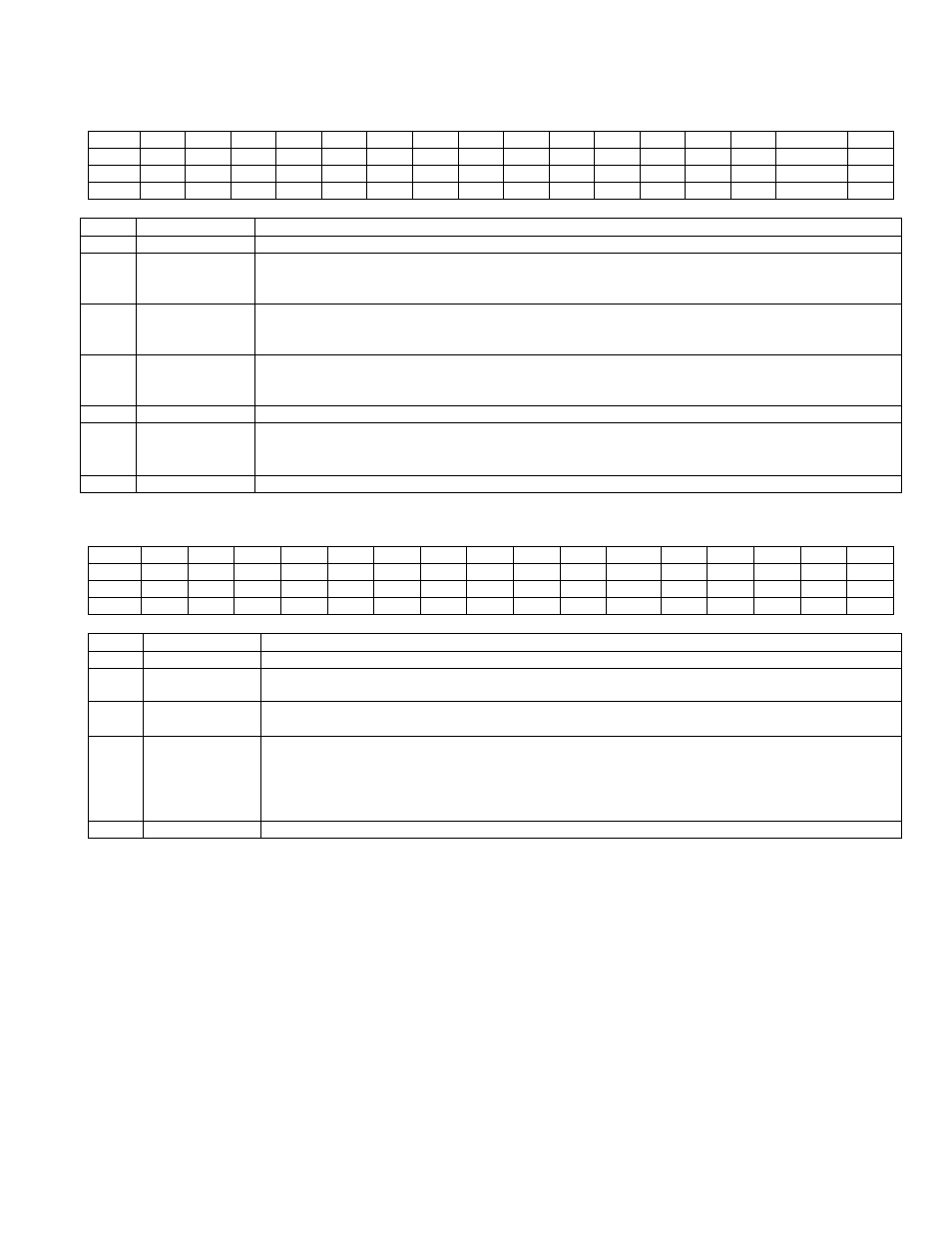

11.2.4 – I

2

C Slave Status2 Register (I2CST2_S)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

-

-

-

-

-

I2CSPI SADI MADI

-

I2CXFRON

-

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

rw

rw

rw

r

rw

r

BIT

NAME

DESCRIPTION

15:6

Reserved

Reserved. The user should not write to these bits.

5

I2CSPI

I

2

C

Slave STOP Interrupt Flag. This bit is set to '1' when a STOP condition is detected. This bit

must be cleared to '0' by software once set. Setting this bit to '1' by software causes an interrupt if

enabled.

4

SADI

I

2

C

START and Start of Address Cycle Flag. This bit is set to ‘1’ if the

I

2

C

controller has detected

an I2C START and 2 cycles of SCL clock. Setting this to ’1’ causes an interrupt if enabled. This bit

must be cleared to ‘0’ by software once set.

3

MADI

Memory Address Detected Interrupt Flag. This bit indicates that the

I

2

C

slave controller has

detected a memory address and copied address into bit [7:0] of MPNTR register. This bit must be

cleared to ‘0’ by software once set. Setting this bit to ‘1’ by software causes an interrupt if enabled.

2

Reserved

Reserved. The user should not write to this bit.

1

I2CXFRON

I

2

C

Slave Transmit Complete Interrupt Flag. This bit indicates that an address or a data byte has

been successfully shifted out and the

I

2

C

controller has received an acknowledgment from the

receiver (NACK or ACK). This bit must be cleared by software once set.

0

Reserved

Reserved. The user should not write to this bit.

11.2.5 – I

2

C Slave Interrupt Enable2 Register (I2CIE2_S)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

-

-

-

-

-

I2CSPIE SADIE MADIE

-

-

-

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

rw

rw

rw

r

rw

r

BIT

NAME

DESCRIPTION

15:6

Reserved

Reserved. The user should not write to these bits.

5

I2CSPIE

I

2

C Slave STOP Interrupt Enable. Setting this bit to ‘1’ causes an interrupt to the CPU when a

STOP condition is detected (I2CSPI=1). Clearing this bit to ‘0’ disables the STOP detection interrupt.

4

SADIE

I

2

C Slave After Start Interrupt Enable. Setting this bit to ‘1’ causes an interrupt to the CPU after

I

2

C

start + two master clocks.

3

MADIE

I

2

C Slave Memory Address Interrupt Enable. Setting this bit to ‘1’ causes an interrupt to the CPU

when a memory address is detected on the

I

2

C

bus. The memory address cycle is detected by

I

2

C

controller after address match with write. The

I

2

C

controller looks for data after address match with

write and copies into the MPNTR register. Clearing this bit to ‘0’ disables the memory address

detection interrupt.

2:0

Reserved

Reserved. The user should not write to these bits.