4 – adc status register (adst1), 5 – adc address register (adaddr), 6 – adc data and configuration register (addata) – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 58: Ds4830a user’s guide

DS4830A User’s Guide

58

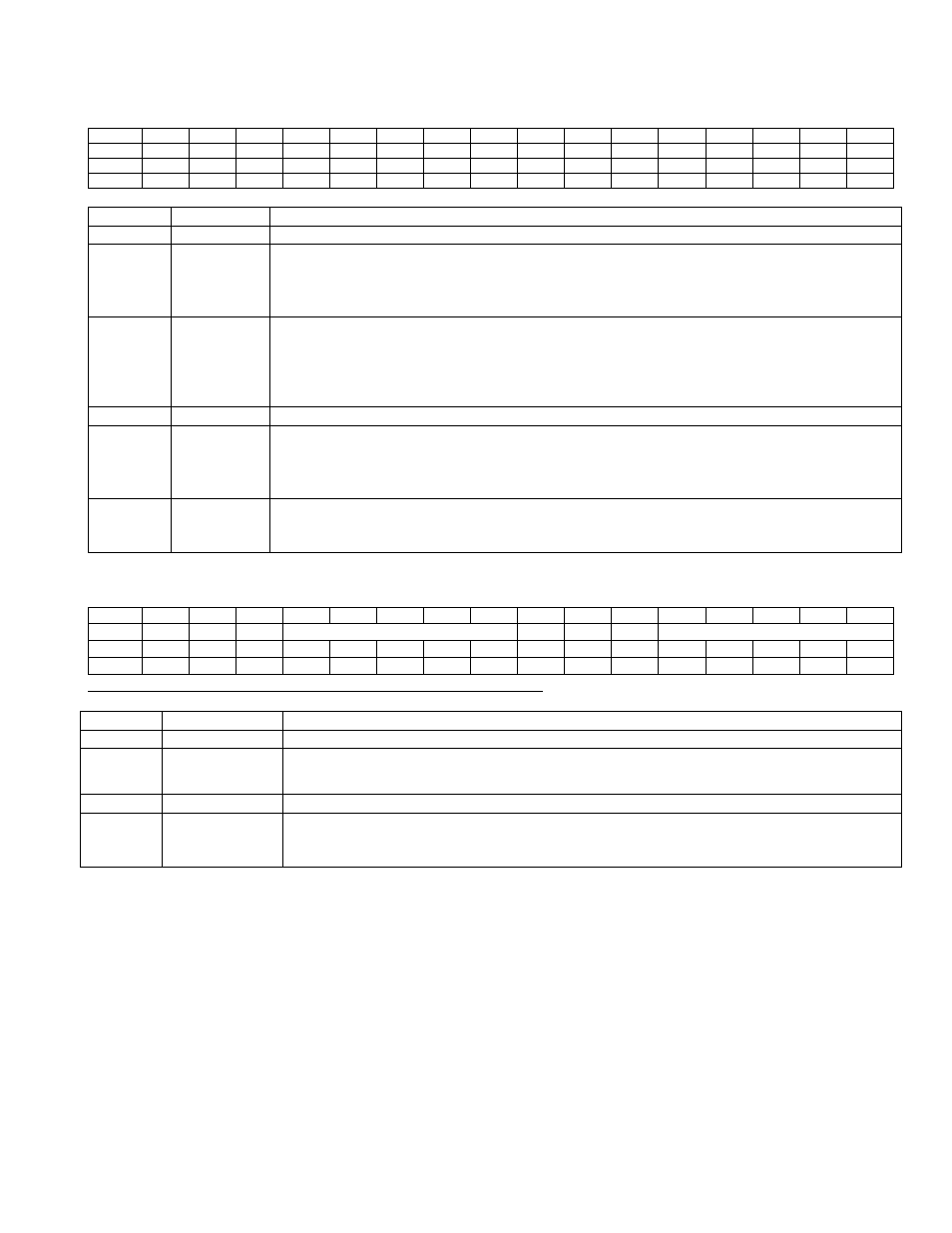

7.2.4 – ADC Status Register (ADST1)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

-

-

-

-

SH1DAI SH0DAI

-

-

INTDAI ADDAI

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

rw

rw

r

r

rw

rw

BIT

NAME

DESCRIPTION

15:6

-

Reserved. The user should not write to these bits.

5

SH1DAI

Sample and Hold 1 Data Available Interrupt Flag. This bit is set to ‘1’ when Sample

and Hold is completed on GP12-GP13 in dual mode and data is ready at buffer location

24. This flag causes an interrupt if the SH1DAI_EN (SHCN.5) is set to ‘1’. This bit is

cleared by software writing a ‘0’.

4

SH0DAI

Sample and Hold 0 Data Available Interrupt Flag. This bit is set to ‘1’ when Sample

and Hold is completed on GP2-GP3 if only S/H0 is used or after completion of S/H1

conversion on GP12-GP13 when both are used in single mode. The S/H0 and S/H1 data

is ready at buffer location 23 and 24 respectively. This flag causes an interrupt if the

SH0DAI_EN (SHCN.1) is set to ‘1’. This bit is cleared by software writing a ‘0’.

3:2

-

Reserved. The user should not write to these bits.

1

INTDAI

Internal Temperature Data Available Interrupt Flag. This bit is set to ‘1’ when an

internal temperature conversion is complete and data is ready in buffer location 22. This

flag causes an interrupt if the INT_IEN (TEMPCN.10) is enabled. This bit is cleared by

software writing a ‘0’.

0

ADDAI

ADC Data Available Interrupt Flag. This bit is set to ‘1’ when the condition matching

ADDAINV bit is met. This flag causes an interrupt if the ADDAIE bit is set. This bit is

cleared by software writing a ‘0’ or when software changes ADCONV bit from '0' to ‘1’.

7.2.5 – ADC Address Register (ADADDR)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

ADSTART[4:0]

-

-

-

ADEND[4:0]

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

rw*

rw*

rw*

rw*

rw*

r

r

r

rw*

rw*

rw*

rw*

rw*

* Unrestricted read, but can only be written to when ADCONV = 0.

BIT

NAME

DESCRIPTION

15:13

-

Reserved. The user should not write to these bits.

12:8

ADSTART[4:0] ADC Conversion Configuration Start Address Bits [4:0]. These bits select the first

conversion configuration register.

7:5

-

Reserved. The user should not write to these bits.

4:0

ADEND[4:0]

ADC Conversion Configuration Ending Address Bits [4:0]. These bits select the

last conversion configuration register. This register is inclusive when defining the

sequence.

7.2.6 – ADC Data and Configuration Register (ADDATA)

The ADDATA register is used to setup the ADC sequence configurations and also to read the results of the ADC

conversions. If the ADST.ADCFG bit is set to a 1 and ADST.ADCAVG = 0, writing to ADDATA writes to one of the

configuration registers. If ADST.ADCFG is set to 0 and ADST.ADCAVG is set to 1, writing to ADDATA writes to one

of the averaging configuration registers. If ADST.ADCFG and ADST.ADCAVG is set to 0, reading from ADDATA

reads one of the conversion results.