2 – timer register descriptions, Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 145

DS4830A User’s Guide

145

16.2 – Timer Register Descriptions

Each General Timer module has three independent SFR registers. These are GTCN, GTV and GTC. The General

Timer Control Register GTCN controls the timer operation. The General Timer Value Register GTV is the Timer

Value register and is incremented every timer clock when enabled. The General Timer Compare Register GTCx is

used in the timer compare mode only. Timer 1 and 2 SFRs are located in module 0 and 3 respectively.

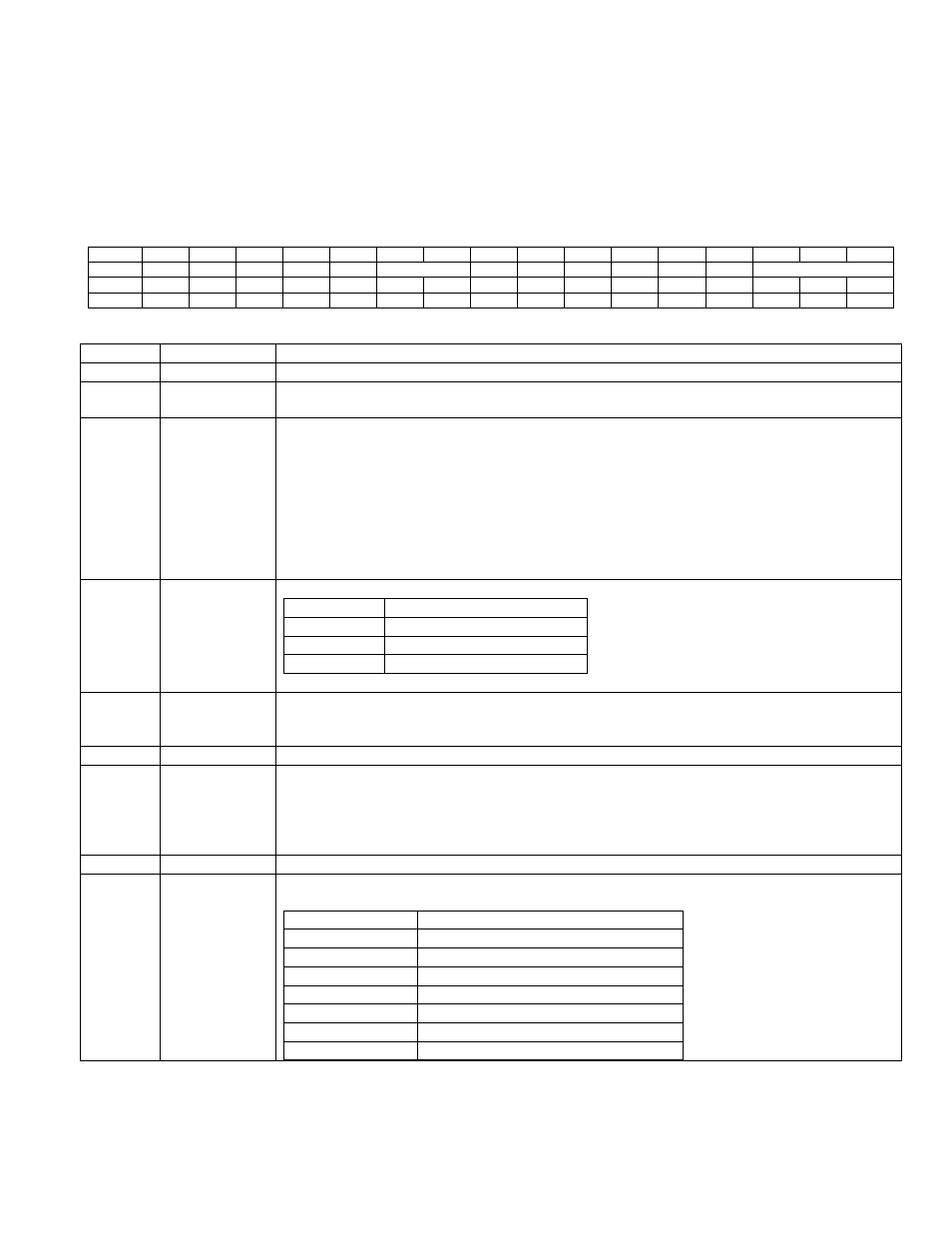

16.2.1 – General Timer Control Register (GTCN)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

GTR

MODE CLK_SEL[1:0]

GTIE

-

-

-

GTIF

-

GTPS[2:0]

Reset*

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

rw

rw

rw

rw

rw

r

r

r

rw

r

rw

rw

rw

*These are default power on reset value.

BIT

NAME

DESCRIPTION

15:13

Reserved

Reserved. The user should write 0 to these bits.

12

GTR

Timer Run Control. Setting this bit to ‘1’ will enable the timer. Clearing this bit to ‘0’ will

stop the timer and clear the GTV register.

11

MODE

Timer Mode Select. This bit selects the timer mode. When this bit is ‘0’, free

synchronous mode is selected. In this mode, the GTV register starts counting from

0x0000. When the GTV register reaches 0xFFFF, GTIF is set to ‘1’ and the GTV register

reloads to 0x0000 at the next timer clock. When the MODE bit is set to ‘1’, compare

mode is selected. In this mode, the GTV register starts counting from 0x0000. When the

GTV register matches the value in the GTC register, GTIF is set to ‘1’ and the GTV

register reloads to 0x0000 at the next timer clock.

Note: In the compare mode, the GTC register value should be set prior to write to the

‘MODE’ bit.

10:9

CLK_SEL[1:0] Timer Clock Select. These bits select the timer clock source.

CLK_SEL

Clock Source

0X

Core Clock

10

Peripheral Clock

11

External Clock*

*The external clock range is 20MHz to 133MHz.

8

GTIE

Timer Interrupt Enable. Setting the GTIE bit to ‘1’ causes an interrupt to be generated

to the CPU when GTIF=1. Clearing this bit to ‘0’ will not cause an interrupt when

GTIF=1.

7:5

Reserved

Reserved. The user should write 0 to these bits.

4

GTIF

Timer Matched Interrupt Flag. This bit is set to ‘1’ when

1. In free synchronous mode, the GTV register value reaches 0xFFFF.

2. In compare mode, the GTV register value matches the value in the GTC register.

This flag generates an interrupt if the GTIE bit is enabled. This bit is cleared in software

by writing ‘0’.

3

Reserved

Reserved. The user should write 0 to these bits.

2:0

GTPS[2:0]

Timer Prescaler Select. These bits configure the prescaler from the timer clock input to

the timer.

Prescaler bits

Timer input clock

000

Timer Clock

001

Timer Clock/4

010

Timer Clock/16

011

Timer Clock/64

100

Timer Clock/256

101

Timer Clock/1024

11X

Timer Clock