Encoder counter status register – Samsung S3F401F User Manual

Page 55

S3F401F_UM_REV1.00

ENCODER COUNTER

4-7

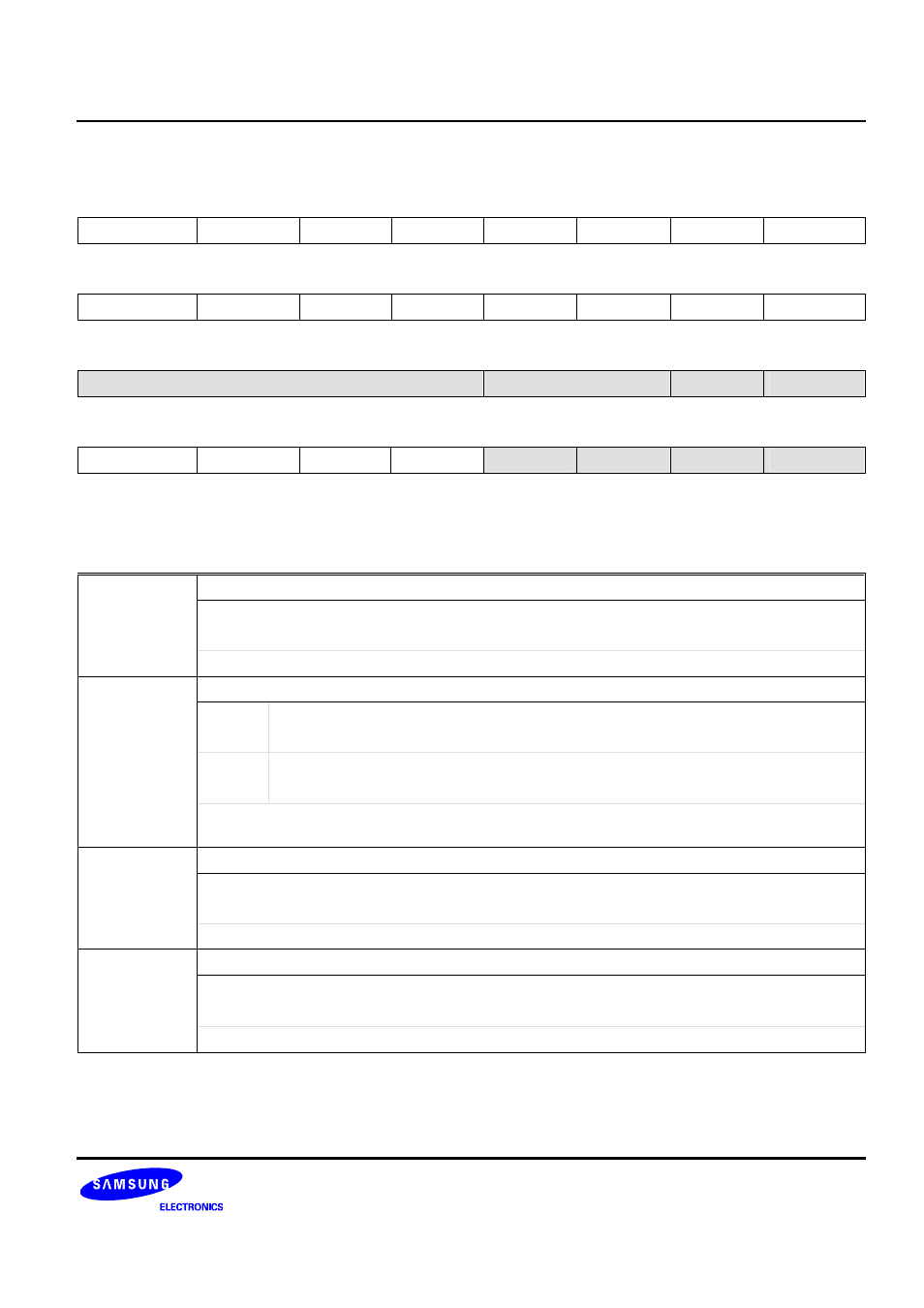

Encoder Counter Status Register

ENCSTATUS (0x008) Access: Read/Write

31 30

29

28

27

26

25

24

−

−

−

−

−

−

−

−

R/W-0 R/W-0

R/W-0

R/W-0

R/W-0 R/W-0 R/W-0 R/W-0

23 22

21

20

19

18

17

16

−

−

−

−

−

−

−

−

R/W-0 R/W-0

R/W-0

R/W-0

R/W-0 R/W-0 R/W-0 R/W-0

15 14

13

12

11

10

9 8

PRESCALEA[15:12]

ESELA[11:10]

PAEN

PACNTCL

R/W-0 R/W-0

R/W-0

R/W-0

R/W-0 R/W-0 R/W-0 R/W-0

7 6

5

4

3

2

1

0

−

−

−

−

PASTAT

PBSTAT

GLITCH

DIRECTION

R/W-0 R/W-0

R/W-0

R/W-0

R/W-0 R/W-0 R/W-0 R/W-0

W: Write

R: Read

-0: 0 After reset

-1: 1 After reset

-U: Undefined after reset

Direction of Motor Rotation Bit

0 = Clockwise - The value of PCNT is increased.

1 = Counter-clockwise - The value of PCNT is decreased.

DIRECTION

Note: This bit is read-only bit.

Glitch Detection Field of Phase A, Phase B and Phase Z

0 = Glitch is not occurred

READ

1 = Glitch is occurred

0 = Glitch bit is cleared

WRITE

1 = No effect

GLITCH

Note: Glitch is detected according to the checking whether if 5 times same level in a row is recognized as

effective signal.

Phase B Status Bit

0 = Low level

1 = High level

PBSTAT

Note: This bit is read only bit.

Phase A Status Bit

0 = Low level

1 = High level

PASTAT

Note: This bit is read only bit.