Uart interrupt mask set/clear register – Samsung S3F401F User Manual

Page 267

S3F401F_UM_REV1.00

UART

12-29

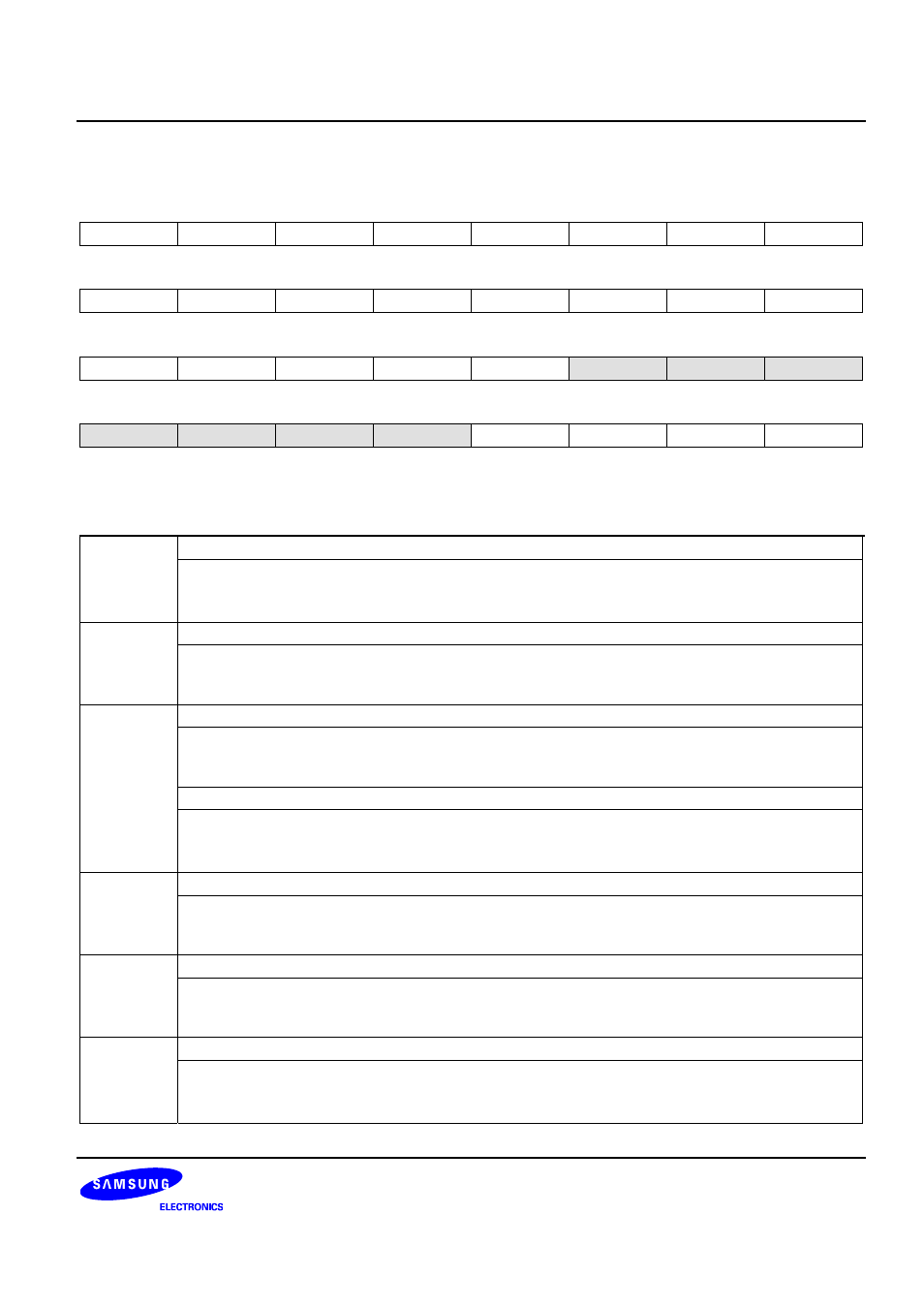

UART Interrupt Mask Set/Clear Register

UARTIMSC (0x038)

Access: Read/Write

31 30 29 28 27 26 25 24

−

−

−

−

−

−

−

−

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

23 22 21 20 19 18 17 16

−

−

−

−

−

−

−

−

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

15 14 13 12 11 10 9 8

−

−

−

−

−

OEIM

BEIM

PEIM

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

7 6 5 4 3 2 1 0

FEIM

RTIM

TXIM

RXIM

−

−

−

−

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

W: Write

R: Read

-0: 0 After reset

-1: 1 After reset

-U: Undefined after reset

RXIM

Receive interrupt mask set/clear bit

On a read: indicates the receive interrupt masking status.

1: mask the receive interrupt (Disable)

0: unmask the receive interrupt (Enable)

TXIM

Transmit interrupt mask set/clear bit

On a read: indicates the transmit interrupt masking status.

1: mask the transmit interrupt (Disable)

0: unmask the transmit interrupt (Enable)

RTIM

Receive timeout interrupt mask set/clear bit

On a read: indicates the receive timeout interrupt masking status.

1: mask the receive timeout interrupt (Disable)

0: unmask the receive timeout interrupt (Enable)

FEIM

Framing error interrupt mask set/clear bit

On a read: indicates the frame error interrupt masking status

1: mask the frame error interrupt (Disable)

0: unmask the frame error interrupt (Enable)

PEIM

Parity error interrupt mask set/clear bit

On a read: indicates the parity error interrupt masking status

1: mask the parity error interrupt (Disable)

0: unmask the parity error interrupt (Enable)

BEIM

Break error interrupt mask set/clear bit

On a read the current mask for the BEIM interrupt is returned.

1: mask the break error interrupt (Disable)

0: unmask the break error interrupt (Enable)

OEIM

Overrun error interrupt mask set/clear bit

On a read: indicates the overrun error interrupt masking status

1: mask the overrun error interrupt (Disable)

0: unmask the overrun error interrupt (Enable)