Power management status register – Samsung S3F401F User Manual

Page 201

S3F401F_UM_REV1.00

POWER MANAGEMENT

9-13

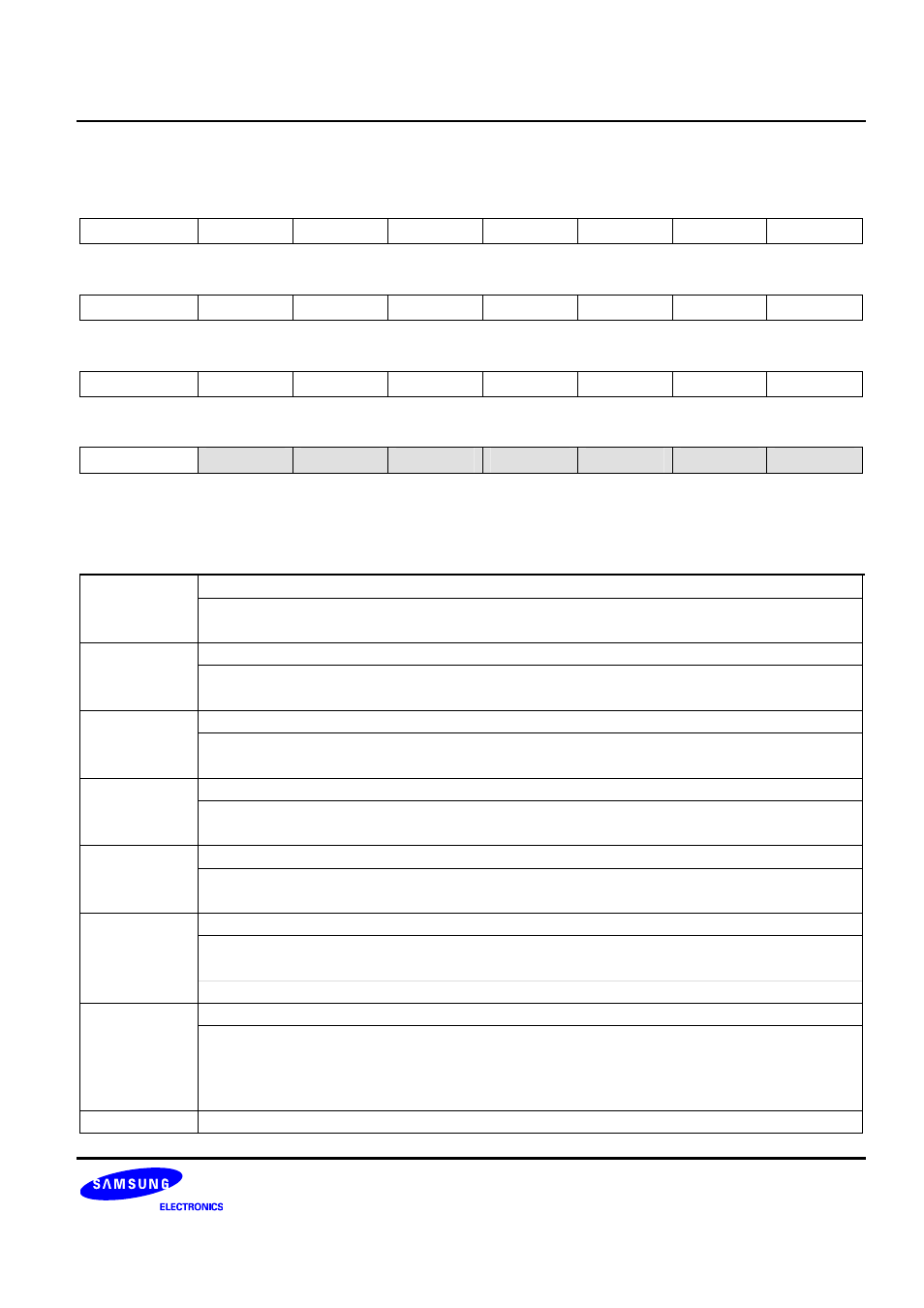

Power Management Status Register

PMSTAT(0x00C)

Access: Read Only

31 30 29 28 27 26 25 24

−

−

−

−

−

−

−

−

R-0 R-0

R-0

R-0

R-0

R-0

R-0

R-0

23 22 21 20 19 18 17 16

−

−

−

−

−

−

−

−

R-0 R-0

R-0

R-0

R-0

R-0

R-0

R-0

15 14 13 12 11 10 9 8

−

−

−

−

−

−

−

−

R-0 R-0

R-0

R-0

R-0

R-0

R-0

R-0

7 6

5

4

3

2

1

0

− (NOTE)

IOSCSTAT

PLLSTAT

CMSTAT

WDTRST

PORRST

PINRST

CMRST

R-1 R-1

R-0

R-0

R-0

R-1

R-1

R-0

W: Write

R: Read

-0: 0 After reset

-1: 1 After reset

-U: Undefined after reset

CMRST

Reset Source by Clock Monitor Bit

0 = The last reset is not caused by the clock monitor.

1 = The last reset is caused by the clock monitor.

PINRST

Reset Source by External Reset Pin

0 = The last reset is not caused by the external reset pin.

1 = The last reset is caused by the external reset pin.

PORRST

Reset Source by POR

0 = The last reset is not caused by the POR.

1 = The last reset is caused by the POR.

WDTRST

Reset Source by Watchdog time

0 = The last reset is not caused by the watchdog timer.

1 = The last reset is caused by the watchdog timer.

CMSTAT External

oscillator status bit

0 = Clock monitor doesn’t detect failure of external oscillator.

1 = Clock monitor detect failure of external oscillator.

PLLSTAT

PLL stabilization status bit

0 = PLL locking timer counter is not matched with PLLLOCKIND.

1 = PLL locking timer counter is matched with PLLLOCKIND.

Note: By this bit, user can know whether the PLL is stabilized or not.

IOSCSTAT Internal

oscillator stabilization status bit

0 = Internal oscillator is not stabilized.

1 = Internal oscillator is stabilized.

The status register of clock & power management, PMSTAT, can be used to recognize reset

source and external clock failure.

NOTE

This bit is only for ‘TEST’.