Port1 data status register – Samsung S3F401F User Manual

Page 177

I/O PORTS

S3F401F_UM_REV1.00

8-28

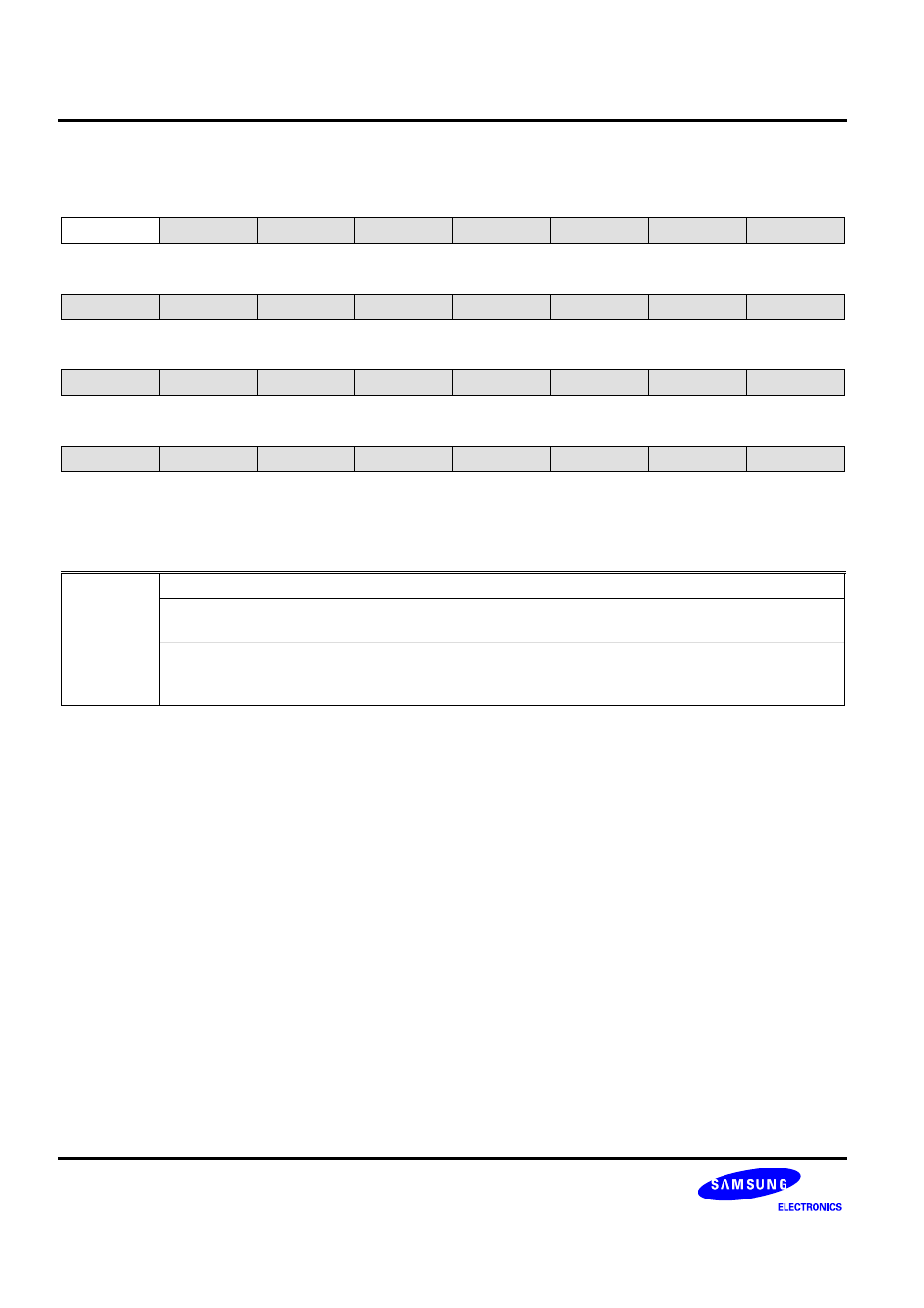

PORT1 Data Status Register

PDATSTAT1 (0x040) Access: Read Only

31 30 29 28 27 26 25 24

−

P1.30

P1.29

P1.28

P1.27

P1.26

P1.25

P1.24

R-U R-U R-U R-U R-U R-U R-U R-U

23 22 21 20 19 18 17 16

P1.23

P1.22

P1.21

P1.20

P1.19 P1.18

P1.17

P1.16

R-U R-U R-U R-U R-U R-U R-U R-U

15 14 13 12 11 10 9 8

P1.15

P1.14

P1.13

P1.12

P1.11

P1.10

P1.9

P1.8

R-U R-U R-U R-U R-U R-U R-U R-U

7 6 5 4 3 2 1 0

P1.7

P1.6

P1.5

P1.4

P1.3

P1.2

P1.1

P1.0

R-U R-U R-U R-U R-U R-U R-U R-U

W: Write

R: Read

-0: 0 After reset

-1: 1 After reset

-U: Undefined after reset

P1 [30:0]

Port 1 Output Data Status Bit

0 = The real level of corresponding pin is at logic 0.

1 = The real level of corresponding pin is at logic 1.

Values read from the address of this register reflect the external state of port 1 not the value

written to this register. Even though the port is configured as a functional pin except ADC, user

can know the external state of port 1 by reading this register.