Adc control register – Samsung S3F401F User Manual

Page 35

A/D CONVERTER

S3F401F_UM_REV1.00

2-8

ADC Control Register

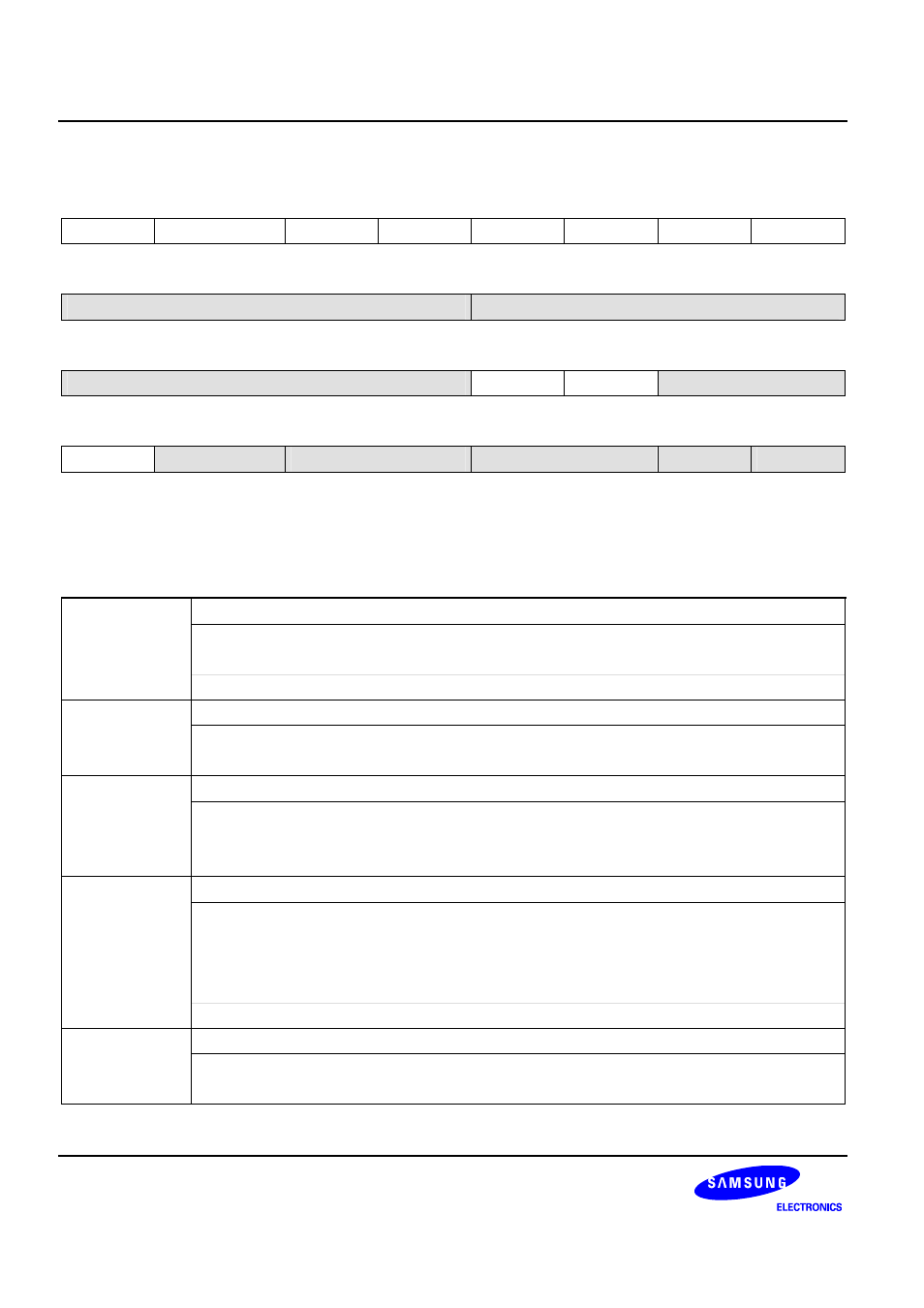

ADCCON (0x000)

Access: Read/Write

31

30

29 28 27 26 25 24

−

−

−

−

−

−

−

−

R/W-0 R/W-0 R/W-0

R/W-0

R/W-0 R/W-0 R/W-0 R/W-0

23

22

21 20 19 18 17 16

SHA3SEL [23:20]

SHA2SEL [17:16]

R/W-0 R/W-0 R/W-0

R/W-0

R/W-0 R/W-0 R/W-0 R/W-0

15

14

13 12 11 10 9 8

SHA1SEL [15:12]

−

−

MODESEL[9:8]

R/W-0 R/W-0 R/W-0

R/W-0

R/W-0 R/W-0 R/W-0 R/W-0

7

6

5 4 3 2 1 0

−

TRIGEDGESEL

CLKSEL[5:4]

TRIGSEL[3:2]

EN

START

R/W-0 R/W-0 R/W-0

R/W-0

R/W-0 R/W-0 R/W-0 R/W-0

W: Write

R: Read

-0: 0 After reset

-1: 1 After reset

-U: Undefined after reset

START

ADC Conversion Start Bit

0 = No effect

1 = Start

Note: This bit is auto-clear bit.

EN

ADC Block Enable Bit

0 = Disable

1 = Enable

TRIGSEL

ADC Start Trigger Signal Selection Field

00 = Software (By ADCCON.0)

01 = Inverter block

1x = ADCTRG pin

CLKSEL

ADC Clock (ADCCLK) Selection Field

000 = Fin

001 = Fin /2

010 = Fin /4

011 = Fin /8

Note: ADCCLK source is

Fin

, not PCLK, and ADCCLK is less than PCLK or equal.

ADC Trigger Edge Selection Bit for ADTRG pin

0 = Falling edge

TRIGEDGESEL

1 = Rising edge