Uart control register – Samsung S3F401F User Manual

Page 264

UART

S3F401F_UM_REV1.00

12-26

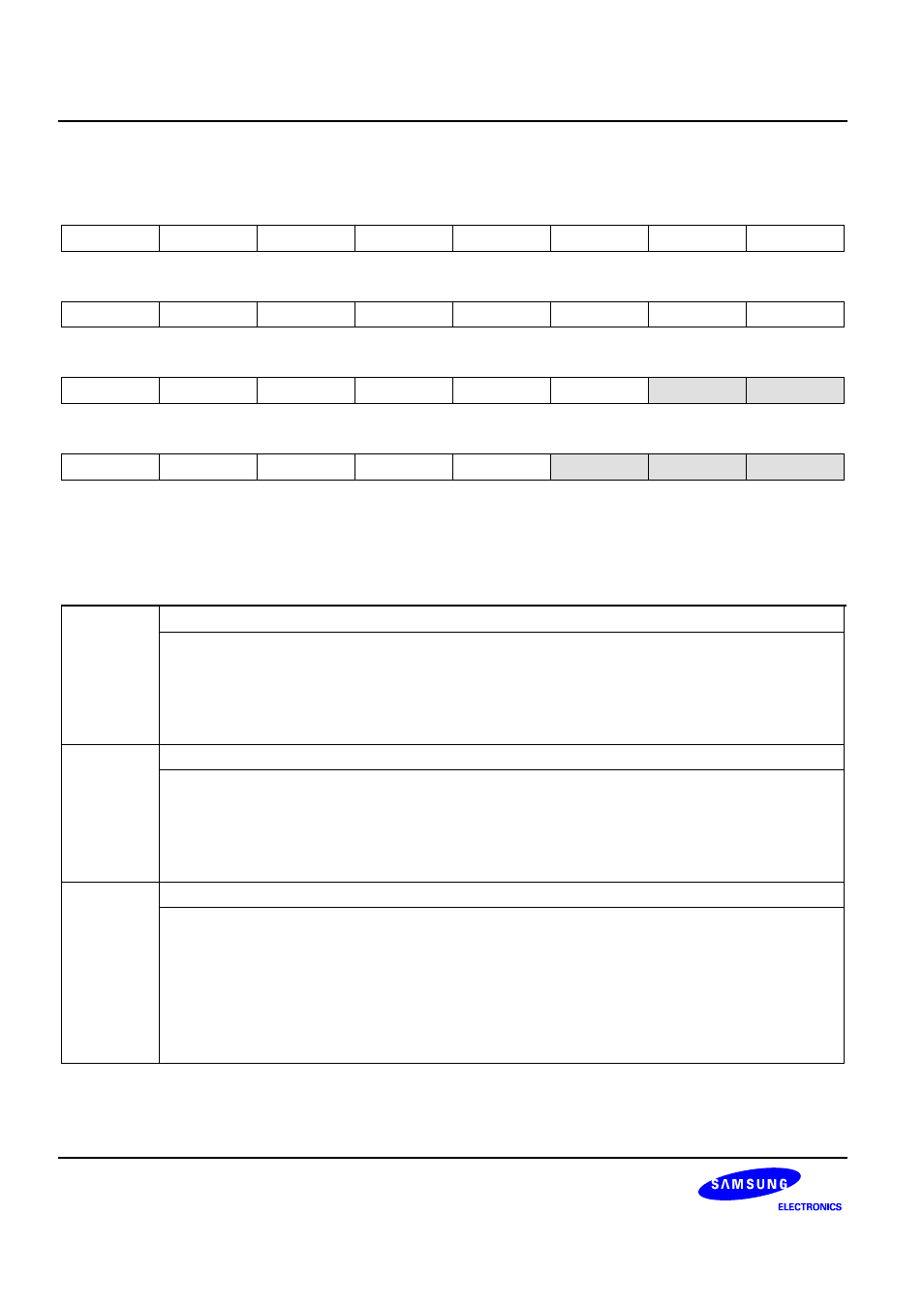

UART Control Register

UARTCR (0x030)

Access: Read/Write

31 30 29 28 27 26 25 24

−

−

−

−

−

−

−

−

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

23 22 21 20 19 18 17 16

−

−

−

−

−

−

−

−

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

15 14 13 12 11 10 9 8

−

−

−

−

−

−

RXE

TXE

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-1 R/W-1

7 6 5 4 3 2 1 0

−

−

−

−

−

SIRLP

SIREN

UARTEN

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

W: Write

R: Read

-0: 0 After reset

-1: 1 After reset

-U: Undefined after reset

UARTEN

UART Enable Bit

0: UART is disabled.

1: the UART is enabled

Data transmission and reception occurs for either UART signals according to the setting of SIR

Enable (bit 1). When the UART is disabled in the middle of transmission or reception, it

completes the current character before stopping.

SIREN

SIR Enable Bit

0: IrDA SIR ENDEC is disabled.

1: IrDA SIR ENDEC is enabled.

This bit has no effect if the UART is not enabled by bit 0 being set to 1. When the IrDA SIR

ENDEC is enabled, data is transmitted and received on nSIROUT and SIRIN. UARTTXD

remains in the marking state (set to 1).Signal transitions on UARTRXD is no effect.

SIRLP

IrDA SIR Low Power Mode Bit

0: selects Non-IrDA encoding mode.

1: selects the IrDA encoding mode.

If this bit is cleared to 0. The low-level bits are transmitted as an active high pulse with a width of

3/16

th

of the bit period.

If this bit is set to 1, low-level bits are transmitted with a pulse width which is 3 times the period of

the IrLPBaud16 input signal, regardless of the selected bit rate. Setting this bit uses less power,

but might reduce transmission distances.