Uart data register – Samsung S3F401F User Manual

Page 253

S3F401F_UM_REV1.00

UART

12-15

UART Data Register

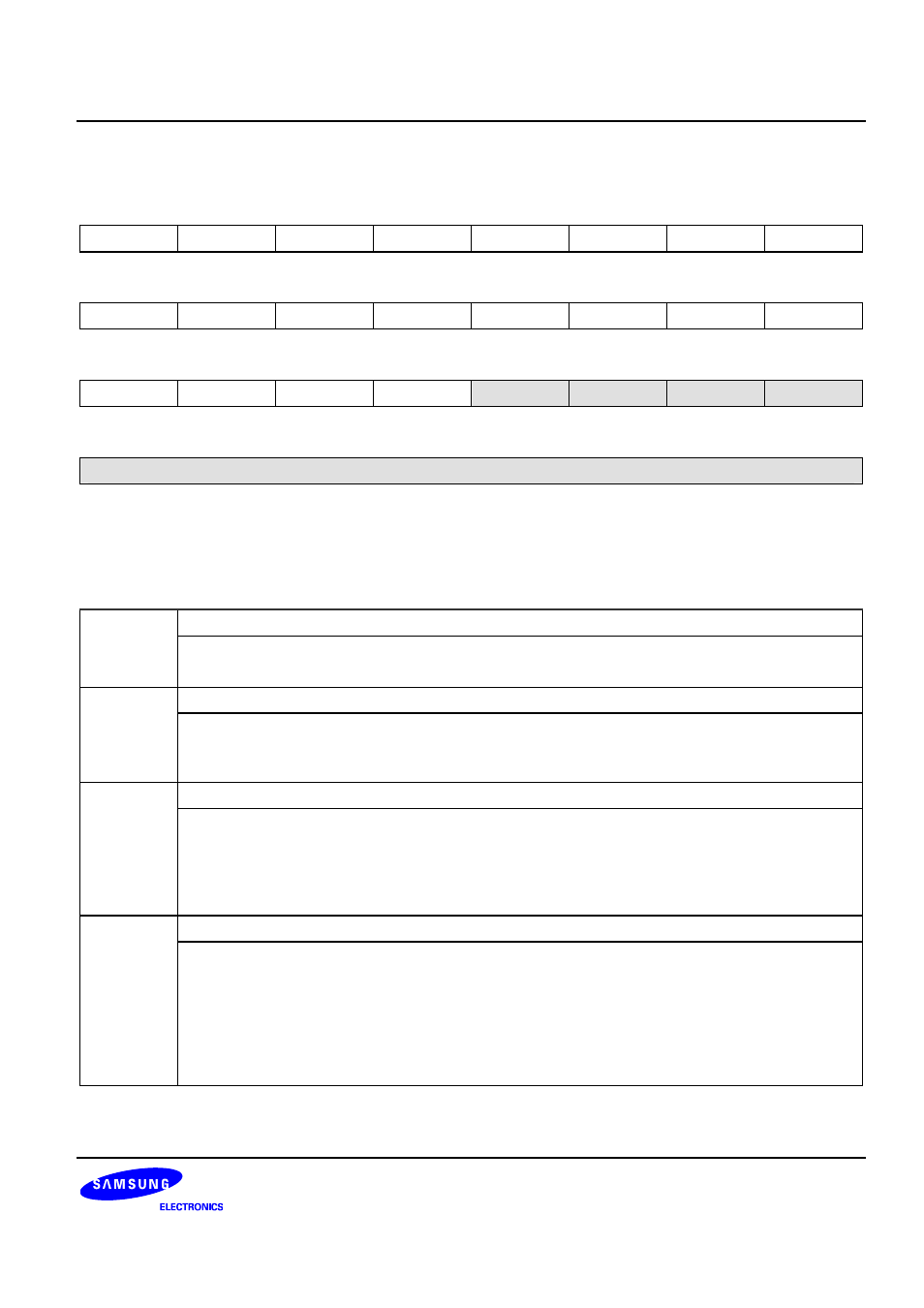

UARTDR (0x000)

Access: Read/Write

31 30 29 28 27 26 25 24

−

−

−

−

−

−

−

−

R/W-U R/W-U R/W-U R/W-U R/W-U R/W-U R/W-U R/W-U

23 22 21 20 19 18 17 16

−

−

−

−

−

−

−

−

R/W-U R/W-U R/W-U R/W-U R/W-U R/W-U R/W-U R/W-U

15 14 13 12 11 10 9 8

−

−

−

−

OE_DR

BE_DR

PE_DR

FE_DR

R/W-U R/W-U R/W-U R/W-U R/W-U R/W-U R/W-U R/W-U

7 6 5 4 3 2 1 0

DATA[7:0]

R/W-U R/W-U R/W-U R/W-U R/W-U R/W-U R/W-U R/W-U

W: Write

R: Read

-0: 0 After reset

-1: 1 After reset

-U: Undefined after reset

DATA

Data Value Field

8-bit data to be received (read)

8-bit data to transmit (write)

FE_DR

Frame Error

0= No frame error during receive

1= Frame error (Interrupt is requested) ex) didn’t have a valid stop bit

In FIFO mode, this error is associated with the character at the top of the FIFO.

PE_DR

Parity Error

0 = No parity error during receive

1 = Parity error(Interrupt is requested)

1: indicates that the parity of the received data character does not match the parity selected as

defined by bits 2 and 7 of the UARTLCR_H register.

In FIFO mode, this error is associated with the character at the top of the FIFO.

BE_DR Break

Error

0 = No break receive

1 = Break receive(Interrupt is requested)

1: if a break condition was detected, indicating that the received data input was held LOW for

longer than a full-word transmission time (defined as start, data, parity and sop bits.) In FIFO

mode, this error is associated with the character at the top of the FIFO. When a break occurs,

only one 0 character is loaded into the FIFO. The next character is only enabled after the receive

data input goes to a 1 (marking state), and the next valid start bit is received.