Uart interrupt fifo level select register – Samsung S3F401F User Manual

Page 266

UART

S3F401F_UM_REV1.00

12-28

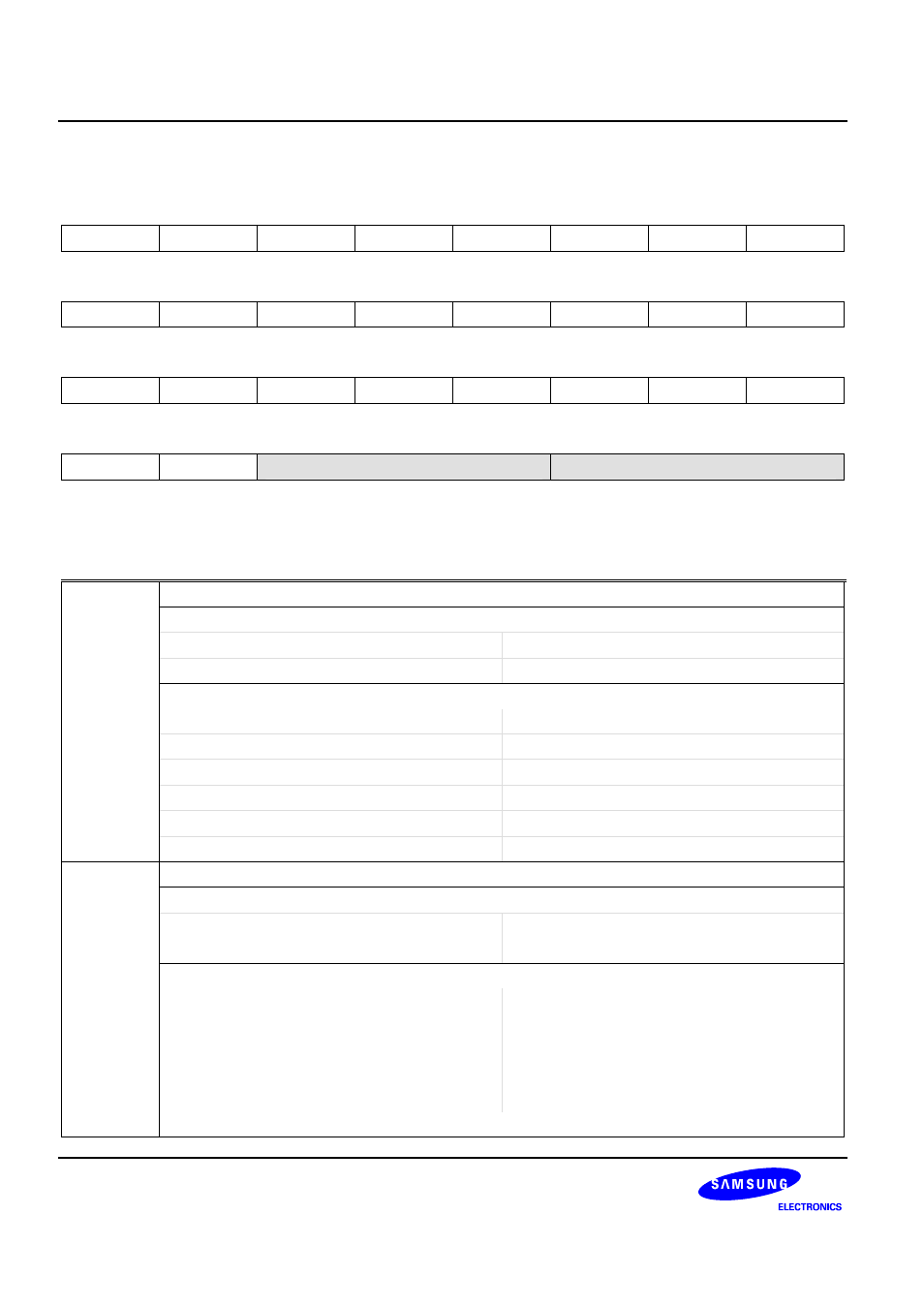

UART Interrupt FIFO Level Select Register

UARTIFLS (0x034)

Access: Read/Write

31 30 29 28 27 26 25 24

−

−

−

−

−

−

−

−

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

23 22 21 20 19 18 17 16

−

−

−

−

−

−

−

−

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

15 14 13 12 11 10 9 8

−

−

−

−

−

−

−

−

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

7 6 5 4 3 2 1 0

−

−

RXIFLSEL[5:3]

TXIFLSEL[2:0]

R/W-0 R/W-0 R/W-0 R/W-1 R/W-0 R/W-0 R/W-1 R/W-0

W: Write

R: Read

-0: 0 After reset

-1: 1 After reset

-U: Undefined after reset

TXIFLSEL

Transmit Interrupt FIFO Level Select Bits

These two bits determine the trigger level of transmit FIFO.

00 = Empty

01 = 4-byte

10 = 8-byte

11 = 12-byte

Define the FIFO level (a trigger point) at which UARTTXINTR are triggered

000 = Transmit FIFO becomes <= 1/8 full FIFO

2bytes

001 = Transmit FIFO becomes <= 1/4 full FIFO

4bytes

010 = Transmit FIFO becomes <= 1/2 full FIFO

8bytes

011 = Transmit FIFO becomes <= 3/4 full FIFO

12bytes

100 = Transmit FIFO becomes <= 7/8 full FIFO

14bytes

101 ~ 111 = Reserved

RXIFLSEL

Receive Interrupt FIFO Level Select Field

These two bits determine the trigger level of receive FIFO.

00 = 4-byte

01 = 8-byte

10 = 12-byte

11 = 16-byte

Define the FIFO level (a trigger point) at which UARTRXINTR are triggered

000 = Receive FIFO becomes >= 1/8 full FIFO

2bytes

001 = Receive FIFO becomes >= 1/4 full FIFO

4bytes

010 = Receive FIFO becomes >= 1/2 full FIFO

8bytes

011 = Receive FIFO becomes >= 3/4 full FIFO

12bytes

100 = Receive FIFO becomes >= 7/8 full FIFO

14bytes

101 ~ 111 = Reserved