System control register – Samsung S3F401F User Manual

Page 196

CLOCK & POWER MANAGEMENT

S3F401F_UM_REV1.00

9-8

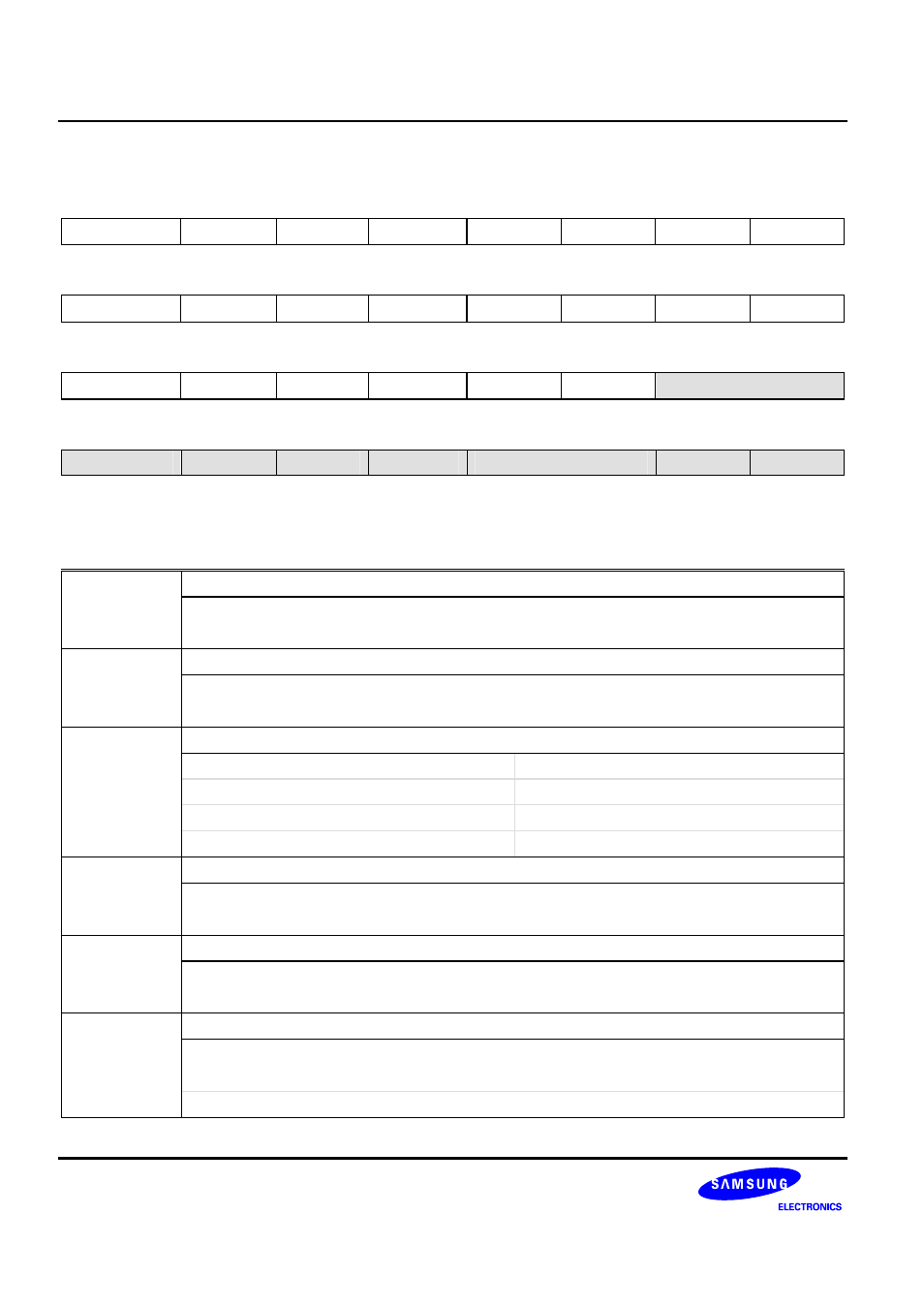

System Control Register

SYSCON (0x000)

Access: Read/Write

31 30

29

28

27

26

25

24

−

−

−

−

−

−

−

−

R/W-0 R/W-0

R/W-0

R/W-0

R/W-0 R/W-0 R/W-0 R/W-0

23 22

21

20

19

18

17

16

−

−

−

−

−

−

−

−

R/W-0 R/W-0

R/W-0

R/W-0

R/W-0 R/W-0 R/W-0 R/W-0

15 14

13

12

11

10

9 8

−

−

−

−

−

−

PCLKDIV [9:8]

R/W-0 R/W-0

R/W-0

R/W-0

R/W-0 R/W-0 R/W-0 R/W-0

7 6 5 4 3 2 1 0

SWRST

IOSCON

PLLON

CLKSRC

MCLKDIV [3:2]

IDLE

STOP

R/W-0 R/W-1

R/W-0

R/W-0

R/W-0 R/W-0 R/W-0 R/W-0

W: Write

R: Read

-0: 0 After reset

-1: 1 After reset

-U: Undefined after reset

STOP

STOP Control Bit

0 = Normal operation

1 = Entering STOP mode

IDLE

IDLE Control Bit

0 = Normal operation

1 = Entering IDLE mode

MCLK Clock Selection Field

00 = SCLK / 8

MCLK

10 = SCLK / 2

MCLK

01 = SCLK / 4

MCLK

MCLKDIV

11 = SCLK

MCLK

CLKSRC

Clock Source Select Bit

0 = EXTCLK

1 = PLL output

PLLON

PLL (Phase Locked Loop) ON/OFF Control Bit

0 = PLL is turned off

1 = PLL is turned on

IOSCON Internal

Oscillator ON/OFF Control Bit

0 = Internal oscillator is turned off.

1 = Internal oscillator is turned on.

Note: Clock monitor is disabled automatically if this bit is set to ‘0’.