Port2 data status register – Samsung S3F401F User Manual

Page 180

S3F401F_UM_REV1.00

I/O

PORTS

8-31

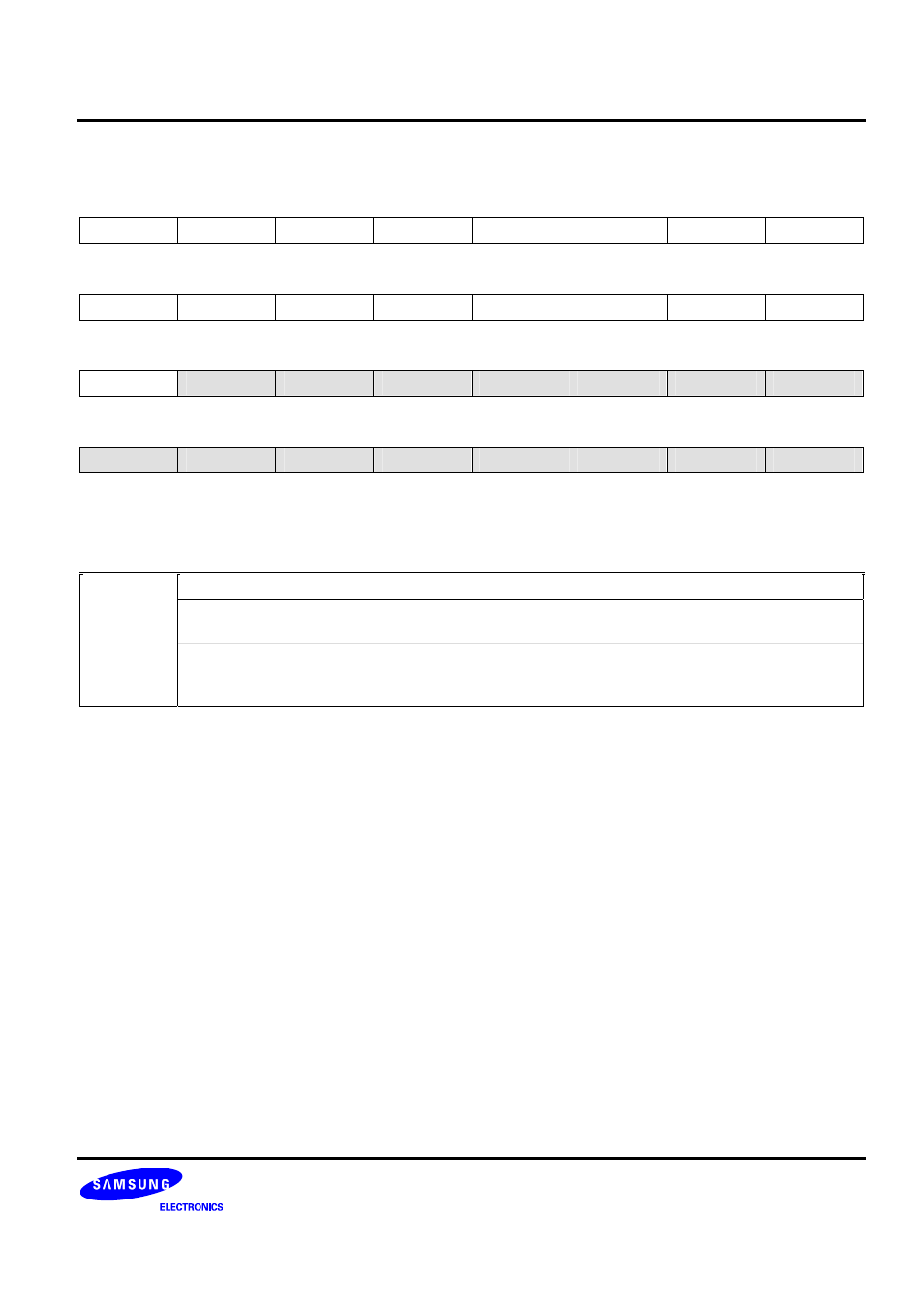

PORT2 Data Status Register

PDATSTAT2 (0x04C) Access: Read Only

31

30

29

28

27

26

25

24

−

−

−

−

−

−

−

−

R-U

R-U

R-U

R-U

R-U

R-U

R-U

R-U

23

22

21

20

19

18

17

16

−

−

−

−

−

−

−

−

R-U

R-U

R-U

R-U

R-U

R-U

R-U

R-U

15

14

13

12

11

10

9

8

−

P2.14

P2.13

P2.12

P2.11

P2.10

P2.9

P2.8

R-U

R-U

R-U

R-U

R-U

R-U

R-U

R-U

7

6

5

4

3

2

1

0

P2.7

P2.6

P2.5

P2.4

P2.3

P2.2

P2.1

P2.0

R-U

R-U

R-U

R-U

R-U

R-U

R-U

R-U

W: Write

R: Read

-0: 0 After reset

-1: 1 After reset

-U: Undefined after reset

P2.[14:0]

Port 2 Output Data Status Bit

0 = The real level of corresponding pin is at logic 0.

1 = The real level of corresponding pin is at logic 1.

Values read from the address of this register reflect the external state of port 2 not the value

written to this register. Even though the port is configured as a functional pin except ADC, user

can know the external state of port 2 by reading this register.

- 100000 (2 pages)

- SPINPOINT MP4 HM320HJ (1 page)

- SPINPOINT MP2 HM201JJ (1 page)

- HN-M750MBB (1 page)

- SH-S223L (33 pages)

- F8274X (324 pages)

- SPINPOINT HS08XJF (1 page)

- DDR3 (21 pages)

- DLP TV SP67L6HX (64 pages)

- M471B1G73AH0 (31 pages)

- BN68-01416A-00 (425 pages)

- SWL-2200C (82 pages)

- SMG-3200 (228 pages)

- SADT-100EC (11 pages)

- SADT-104WM (12 pages)

- G2 PORTABLE HX-MU025DC (1 page)

- TruDirect BG68-01526A (9 pages)

- SADT-100HM (8 pages)

- TS-H663D (33 pages)

- MUXONENAND A-DIE KFN4G16Q2A (173 pages)

- SPINPOINT HS120JR (1 page)

- TrueDirect SH-S203S (16 pages)

- COMBO DRIVE SM-316 (10 pages)

- M391B5273DH0 (36 pages)

- SWL-2210P (67 pages)

- SC-140 (4 pages)

- TS-HB33 (31 pages)

- Color Dual Quad Network Observation System SSC21WEB (103 pages)

- BF68-00160B (60 pages)

- RIF-BT10 (17 pages)

- TS-HB43L (37 pages)

- TS-H292A (25 pages)

- Computer Drive (1 page)

- CAPLIO 400G (1 page)

- SWL-3000AP (88 pages)

- SCS-26UC4 (67 pages)

- SCS-26UC4 (6 pages)

- SWL-2100N (75 pages)

- SH-S223C (34 pages)

- FLEX-MUXONENAND KFM4GH6Q4M (142 pages)

- SNS-100/400 (38 pages)

- SWL-4000AP (89 pages)

- iDCS 500-DCS (32 pages)

- SN-324 (5 pages)