2 match & overflow mode operation – Samsung S3F401F User Manual

Page 228

TIMER

S3F401F_UM_REV1.00

11-4

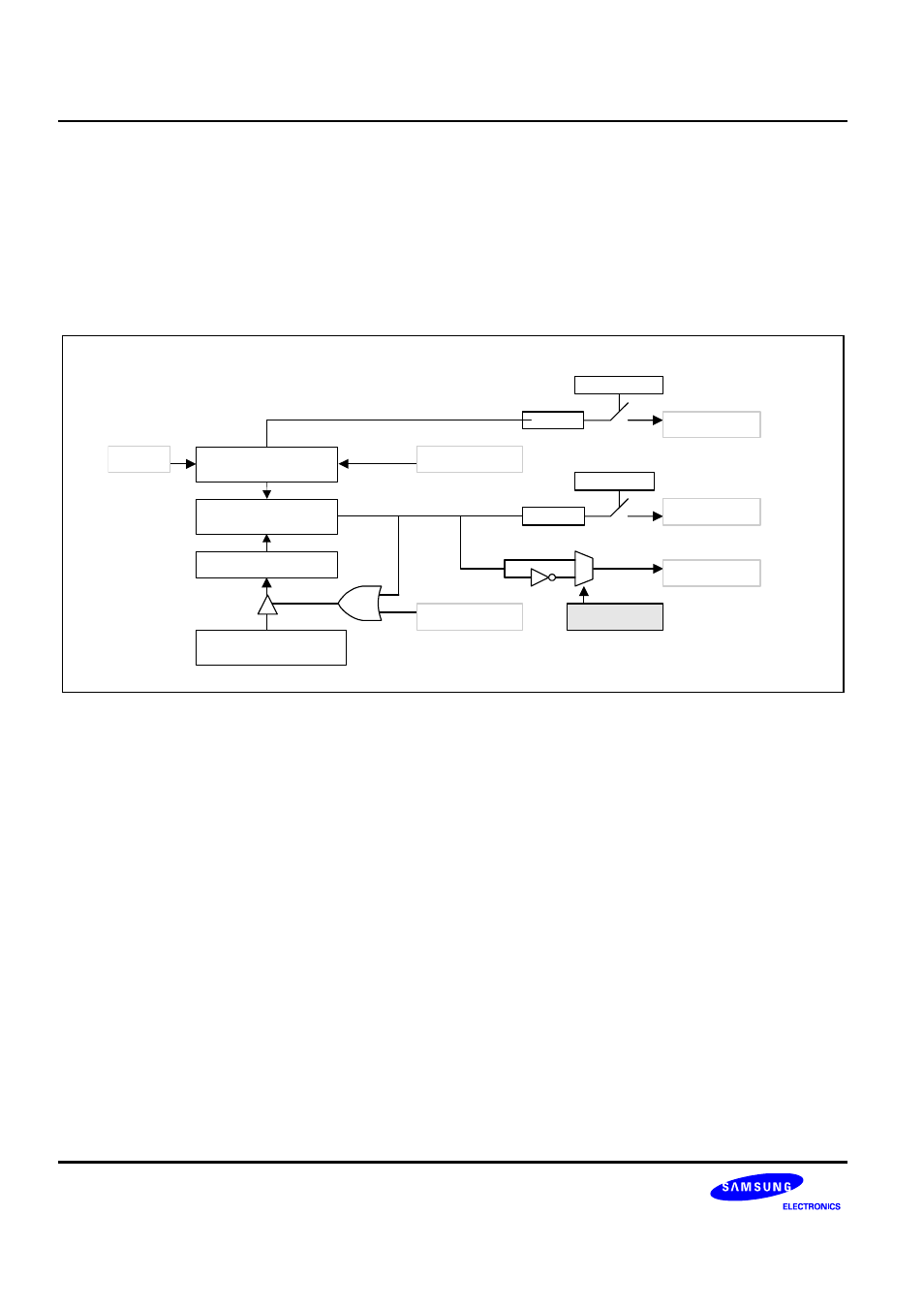

2.2 MATCH & OVERFLOW MODE OPERATION

In this mode, a match signal can be generated when the counter value is identical to the value written to the timer

data register. However, the match signal does not clear the counter even if it can generate a match interrupt as

same as the interval mode. Because it does not clear the counter value, the timer can run up to the overflow of

counter value and generate an overflow interrupt, also. After the overflow of counter value, the counter value will be

counted from 0x0000, again. As soon as starting this operation by start and CL signal, timer spends three-clocks for

synchronization with system clock. The timer starts counting after three-clock.

Match

Clear

TCNT.15-.0:

CNT

16-Bit Counter

16-Bit Comparator

Buffer Register

TDAT.15-.0:

DATA

Timer Data Register

INTMASK

INTPND

TCON.1:

IVT

INTPND

Overflow

TCNK

TCON.6:

CL

TCON.6:

CL

INT_TMCn

TnPWM

INTMASK

INT_TOFn

Figure 11-3. Simplified Timer Function Diagram: Match & Overflow Timer Mode