Interrupt mask 2 register – Samsung S3F401F User Manual

Page 141

S3F401F_UM_REV1.00

INTERRUPT CONTROLLER

7-17

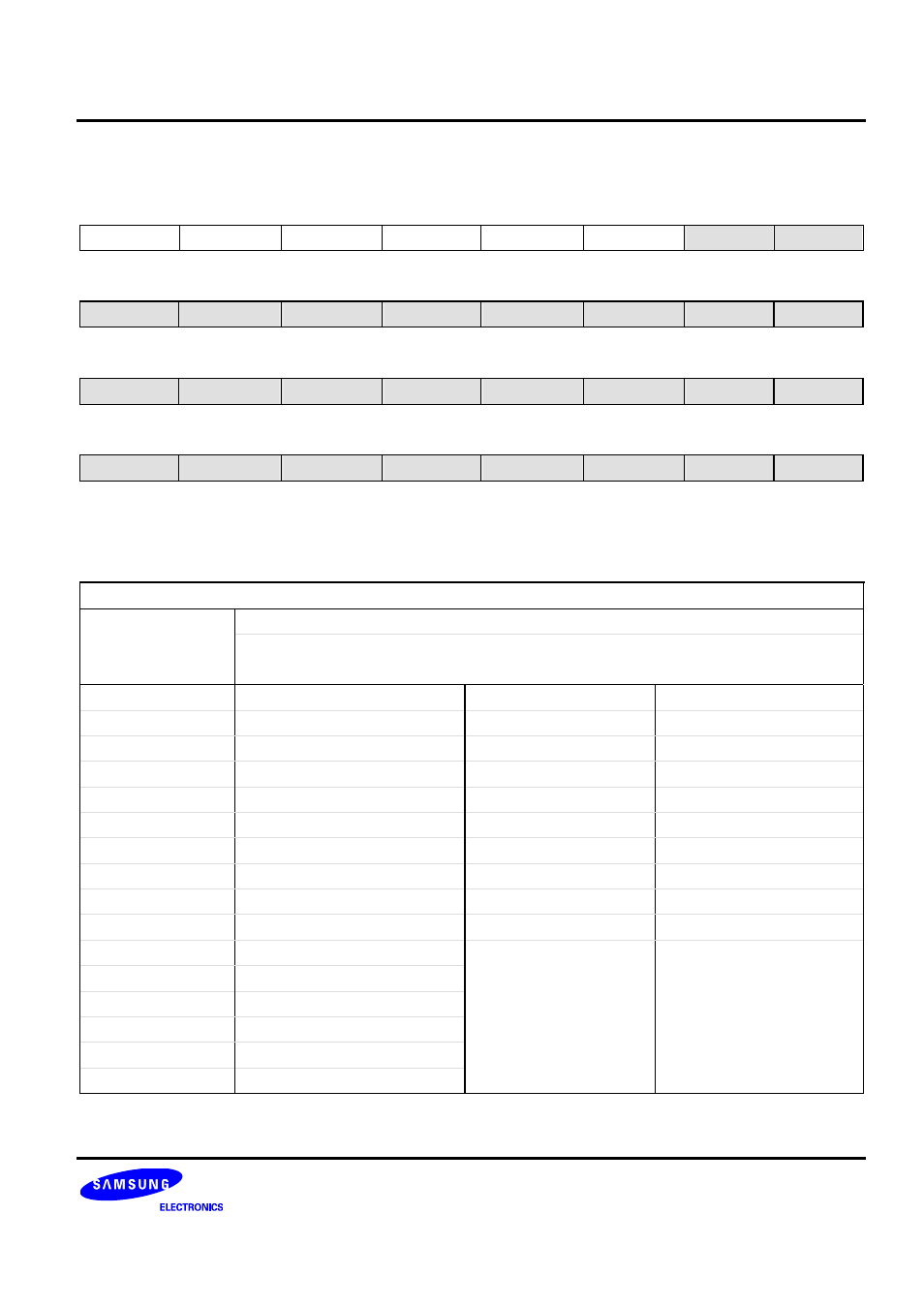

INTERRUPT MASK 2 Register

INTMSK2 (0x020)

Access: Read/Write

31 30 29 28 27 26 25

24

−

−

−

−

−

−

SW0_MSK

BT_MSK

R/W R/W R/W R/W R/W R/W

R/W-0

R/W-0

23 22 21 20 19 18 17

16

SSP_ERR1_MSK SSP_RX1_MSK

SSP_TX1_MSK SSP_ERR0_MSK SSP_RX0_MSK

SSP_TX0_MSK

TMC5_MSK

TOF5_MSK

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

R/W-0

15 14 13 12 11 10 9 8

TMC4_MSK

TOF4_MSK

TMC3_MSK

TOF3_MSK

TMC2_MSK

TOF2_MSK

TMC1_MSK

TOF1_MSK

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

R/W-0

7 6 5 4 3 2 1

0

TMC0_MSK

TOF0_MSK

UERR1_MSK

UTX1_MSK

URX1_MSK

UERR0_MSK UTX0_MSK

URX0_MSK

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

R/W-0

W: Write

R: Read

-0: 0 After reset

-1: 1 After reset

-U: Undefined after reset

Interrupt Mask Register 2

Each bit can disable or enable the corresponding interrupt request

0 = Interrupt service is masked or disabled.

INTMSK2

1 = Interrupt service is available.(Unmasked)

URX0_MSK 0x0000_0001

TOF5_MSK

0x0001_0000

UTX0_MSK 0x0000_0002

TMC5_MSK

0x0002_0000

UERR0_MSK 0x0000_0004

SSP_TX0_MSK 0x0004_0000

URX1_MSK 0x0000_0008

SSP_RX0_MSK 0x0008_0000

UTX1_MSK 0x0000_0010

SSP_ERR0_MSK

0x0010_0000

UERR1_MSK 0x0000_0020

SSP_TX1_MSK 0x0020_0000

TOF0_MSK 0x0000_0040

SSP_RX1_MSK 0x0040_0000

TMC0_MSK 0x0000_0080

SSP_ERR1_MSK

0x0080_0000

TOF1_MSK 0x0000_0100

BT_MSK

0x0100_0000

TMC1_MSK 0x0000_0200

SW0_MSK

0x0200_0000

TOF2_MSK 0x0000_0400

TMC2_MSK 0x0000_0800

TOF3_MSK 0x0000_1000

TMC3_MSK 0x0000_2000

TOF4_MSK 0x0000_4000

TMC4_MSK 0x0000_8000