Uart flag register – Samsung S3F401F User Manual

Page 257

S3F401F_UM_REV1.00

UART

12-19

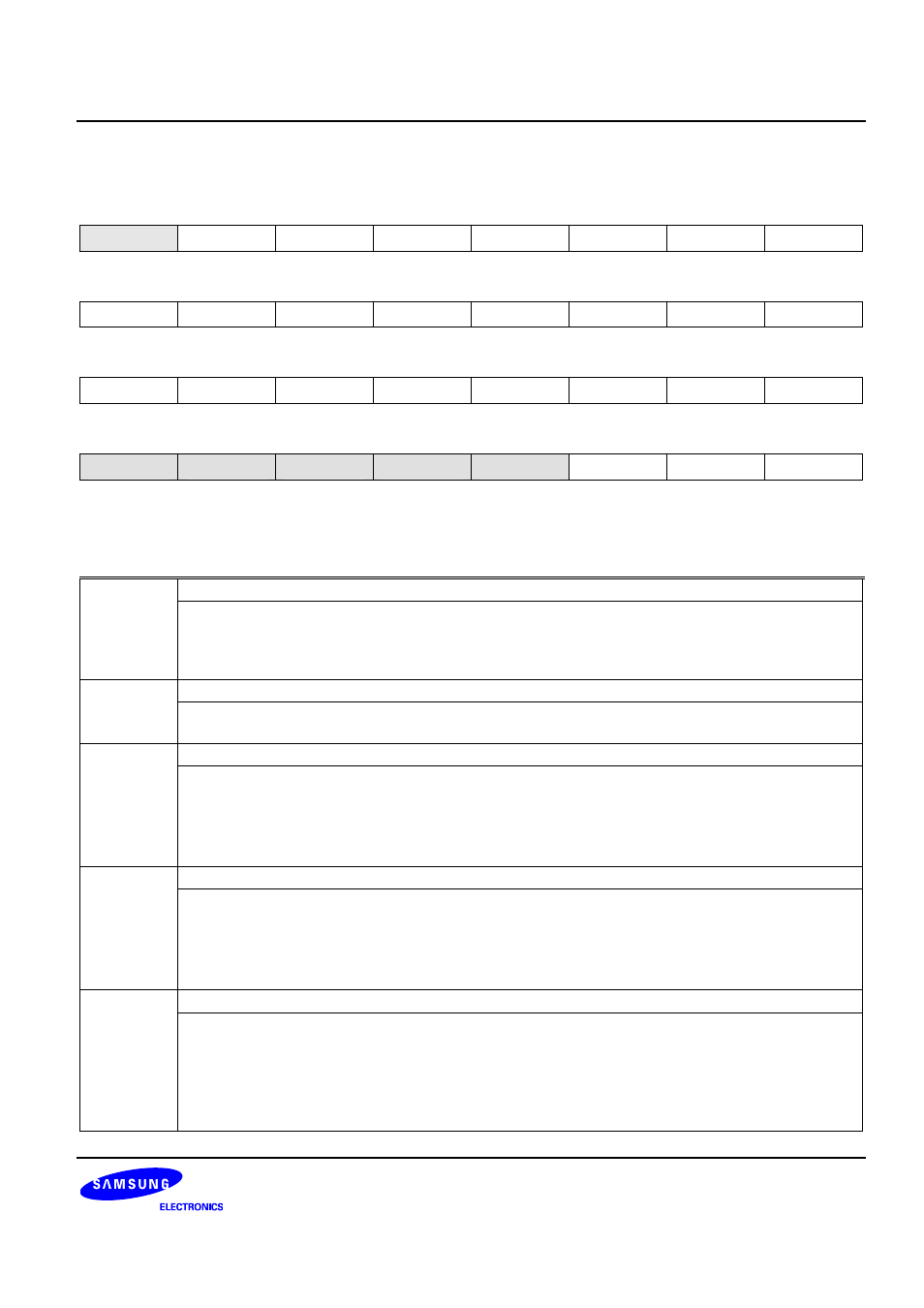

UART Flag Register

UARTFR (0x018)

Access: Read Only

31 30 29 28 27 26 25 24

DBGEN

−

−

−

−

−

−

−

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

23 22 21 20 19 18 17 16

−

−

−

−

−

−

−

−

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

15 14 13 12 11 10 9 8

−

−

−

−

−

−

−

−

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

7 6 5 4 3 2 1 0

TXFE

RXFF

TXFF

RXFE

BUSY

−

−

−

R-1 R-0 R-0 R-1 R-0 R-0 R-0 R-0

W: Write

R: Read

-0: 0 After reset

-1: 1 After reset

-U: Undefined after reset

BUSY

UART Busy

1: the UART is busy transmitting data. This bit remains set until the complete byte, including all

the stop bits, has been sent from the shift register.

This bit is set as soon as the transmit FIFO becomes non-empty (regardless of whether the

UART is enabled or not).

RXFE

Receive FIFO Empty

If the FIFO is disabled, this bit is set when the receive holding register is empty.

If the FIFO is enabled, the RXFE bit is set when the receive FIFO is empty.

TXFF

Transmit FIFO Full

This bit is automatically set to 1 whenever transmit FIFO is full during transmit operation

0 = 0-byte

≤ Tx FIFO data ≤ 15-byte

1 = Full

If the FIFO is disabled, this bit is set when the transmit holding register is full.

If the FIFO is enabled, the TXFF bit is set when the transmit FIFO is full.

RXFF

Receive FIFO Full

This bit is automatically set to 1 whenever receive FIFO is full during receive operation

0 = 0-byte

≤ Rx FIFO data ≤ 15-byte

1 = Full

If the FIFO is disabled, this bit is set when the receive holding register is full.

If the FIFO is enabled, the RXFF bit is set when the receive FIFO is full.

TXFE

Transmit FIFO Empty

This bit is automatically set to 1 when the transmit buffer register has no valid data to transmit

and the transmit shift register is empty.

0 = Not empty

1 = Transmit buffer & shifter register empty

If the FIFO is disabled, this bit is set when the transmit holding register is empty.

If the FIFO is enabled, the RXFE bit is set when the transmit FIFO is empty.