Samsung S3F401F User Manual

Page 54

ENCODER COUNTER

S3F401F_UM_REV1.00

4-6

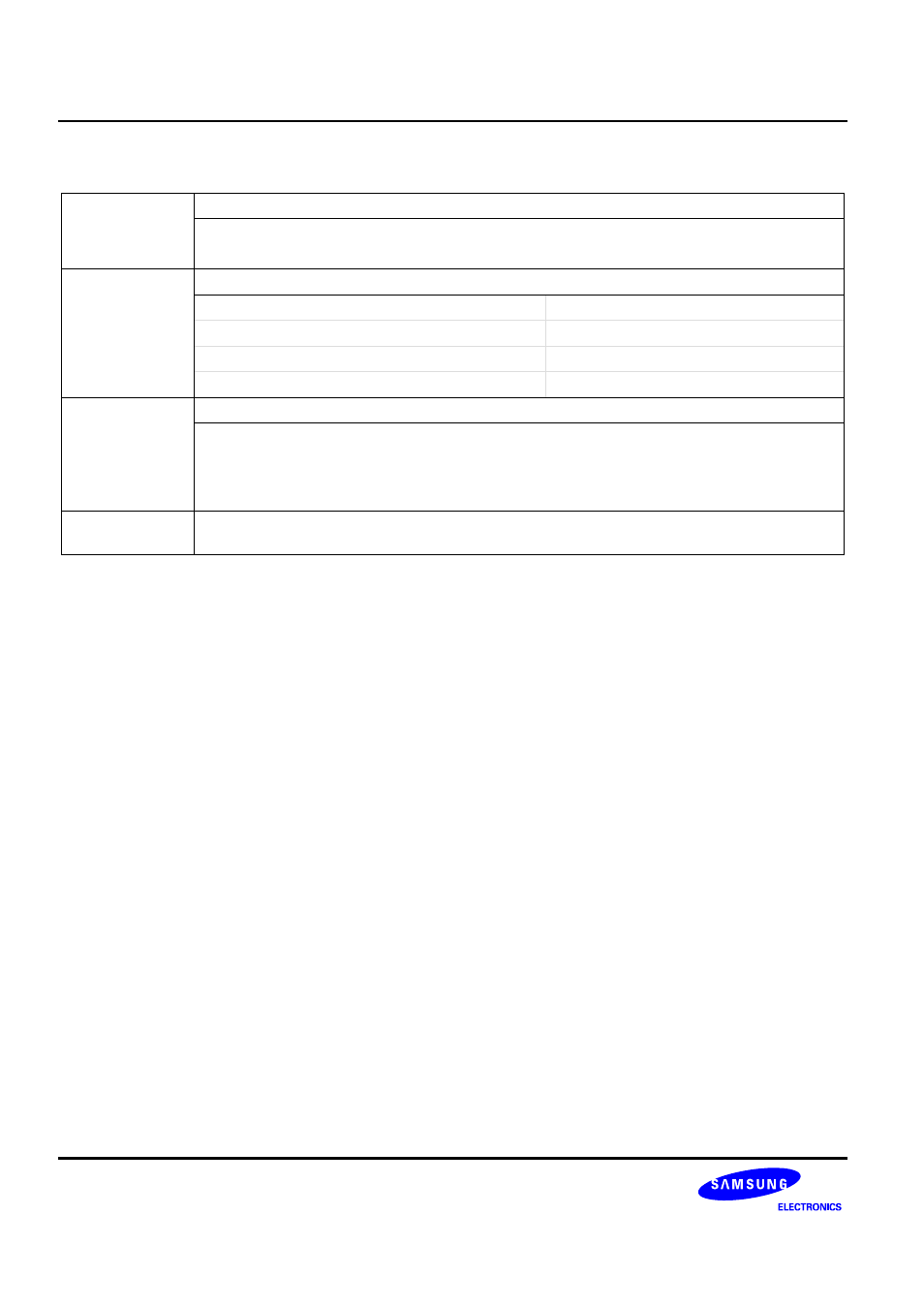

Encoder Counter Control Register 0 (Continued) ENCCON0 (0x000)

Access: Read/Write

PZCLEN

PCNT Clear Enable by Phase Z.

0 = Enable

1 = Disable

ENCCLKSEL

Encoder Counter Clock (DECCLK) Selection Field

000 = ENCCLK

100 = ENCCLK /16

001 = ENCCLK /2

101 = ENCCLK /32

010 = ENCCLK /4

110 = ENCCLK /64

011 = ENCCLK /8

111 = ENCCLK /128

DBGEN

Debug Enable Bit

0 = ENC is halted during processor debug mode.

1 = ENC is not halted during processor debug mode. Although you break the debugger, you

can see count register and several bits of status register changing according to the operation

setting.

NOTE

Several bits of status - These bits are ENCSTATUS.0, ENCSTATUS.2 and ENCSTATUS.3. Because

these bits can a read-only bit.

- 100000 (2 pages)

- SPINPOINT MP4 HM320HJ (1 page)

- SPINPOINT MP2 HM201JJ (1 page)

- HN-M750MBB (1 page)

- SH-S223L (33 pages)

- F8274X (324 pages)

- SPINPOINT HS08XJF (1 page)

- DDR3 (21 pages)

- DLP TV SP67L6HX (64 pages)

- M471B1G73AH0 (31 pages)

- BN68-01416A-00 (425 pages)

- SWL-2200C (82 pages)

- SMG-3200 (228 pages)

- SADT-100EC (11 pages)

- SADT-104WM (12 pages)

- G2 PORTABLE HX-MU025DC (1 page)

- TruDirect BG68-01526A (9 pages)

- SADT-100HM (8 pages)

- TS-H663D (33 pages)

- MUXONENAND A-DIE KFN4G16Q2A (173 pages)

- SPINPOINT HS120JR (1 page)

- TrueDirect SH-S203S (16 pages)

- COMBO DRIVE SM-316 (10 pages)

- M391B5273DH0 (36 pages)

- SWL-2210P (67 pages)

- SC-140 (4 pages)

- TS-HB33 (31 pages)

- Color Dual Quad Network Observation System SSC21WEB (103 pages)

- BF68-00160B (60 pages)

- RIF-BT10 (17 pages)

- TS-HB43L (37 pages)

- TS-H292A (25 pages)

- Computer Drive (1 page)

- CAPLIO 400G (1 page)

- SWL-3000AP (88 pages)

- SCS-26UC4 (6 pages)

- SCS-26UC4 (67 pages)

- SWL-2100N (75 pages)

- SH-S223C (34 pages)

- FLEX-MUXONENAND KFM4GH6Q4M (142 pages)

- SNS-100/400 (38 pages)

- SWL-4000AP (89 pages)

- iDCS 500-DCS (32 pages)

- SN-324 (5 pages)