Samsung S3F401F User Manual

Page 254

UART

S3F401F_UM_REV1.00

12-16

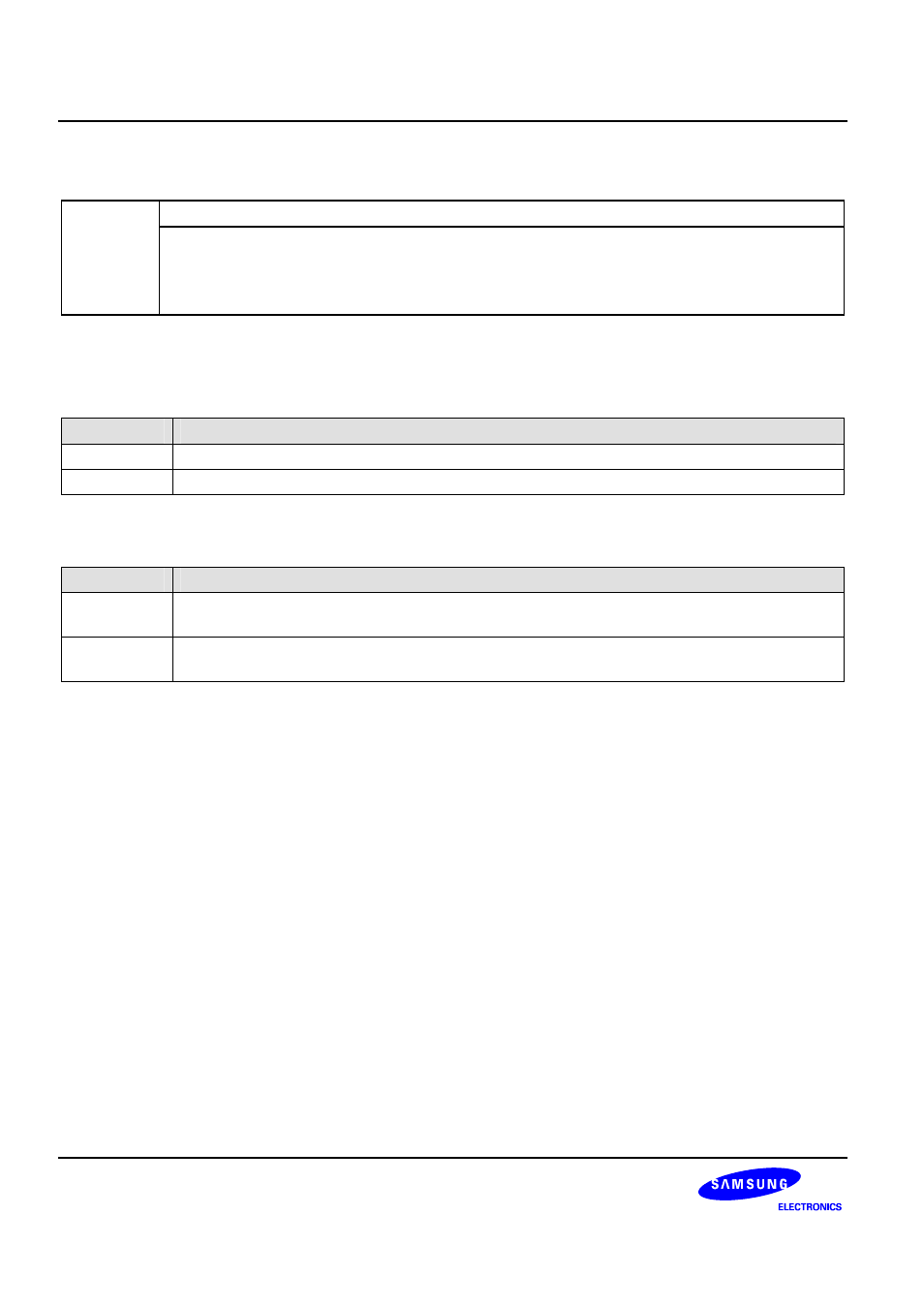

UART Data Register (Continued)

UARTDR (0x000)

Access: Read/Write

OE_DR Overrun

Error

0 = No overrun error during receive

1 = Overrun error(Interrupt is requested)

1: if data is received and the receive FIFO is already full. This is cleared to 0 once there is an

empty space in the FIFO and a new character can be written to it.

This bit is automatically set to ‘1’ whenever frame, parity, break and overrun errors occur during receive operation.

NOTE:

You must disable the UART before any of the control registers are reprogrammed. When the UART is

disabled in the middle of transmission or reception, it completes the current character before stopping.

FIFO

For Words to be Transmitted

Enable

data written to this location is pushed onto the transmit FIFO

Disable

data is stored in the transmitter holding register (the bottom word of the transmit FIFO)

The write operation initiates transmission from the UART. The data is prefixed with a start bit, appended with the

appropriate parity bit (if parity is enabled), and a stop bit. The resultant word is then transmitted.

FIFO

For Received Words

Enable

The data byte and the 4-bit status(break, frame, parity, and overrun) is pushed onto the

12-bit wide receive FIFO

Disable

The data byte and status are stored in the receiving holding register (the bottom

word of the receive FIFO).

The received data byte is read by performing reads from the UARTDR register along with the corresponding

status information. The status information can also be read by a read of the UARTRSR/UARTECR register.