Status registers – AMETEK BPS Series Programming Manual User Manual

Page 165

BPS / MX / RS Series SCPI Programming Manual

AMETEK Programmable Power

Manual P/N 7003-961 Rev. AA

165

7.

Status Registers

You can use status register programming to determine the operating condition of the AC

source at any time. For example, you may program the AC source to generate an interrupt

(assert SRQ) when an event such as a current limit occurs. When the interrupt occurs, your

program can then act on the event in the appropriate fashion.

Figure 7-1 shows the status register structure of the AC/DC source. Table 5-1 defines the

status bits. The Standard Event, Status Byte, and Service Request Enable registers as well

as the Output Queue perform standard IEEE-488 functions as defined in the IEEE 488.2

Standard Digital Interface for Programmable Instrumentation. The Operation Status, and the

Questionable Status registers, implement functions that are specific to the AC/DC source.

7.1

Power-On Conditions

All status register groups are cleared at power on. This means all data bits and all Event

Enable register bits are cleared. It is possible however the set the PON mask in the Event

enable register to cause a SRQ. This can be accomplished using the *PSC command. Once

set, this condition is retained in non-volatile memory and will be recalled when power is

applied to the AC/DC source. See paragraph 5.7 for details on the use of the *PSC

command.

7.2

Operation Status Group

The Operation Status group records signals that occur during normal operation. The group

consists of the following registers:

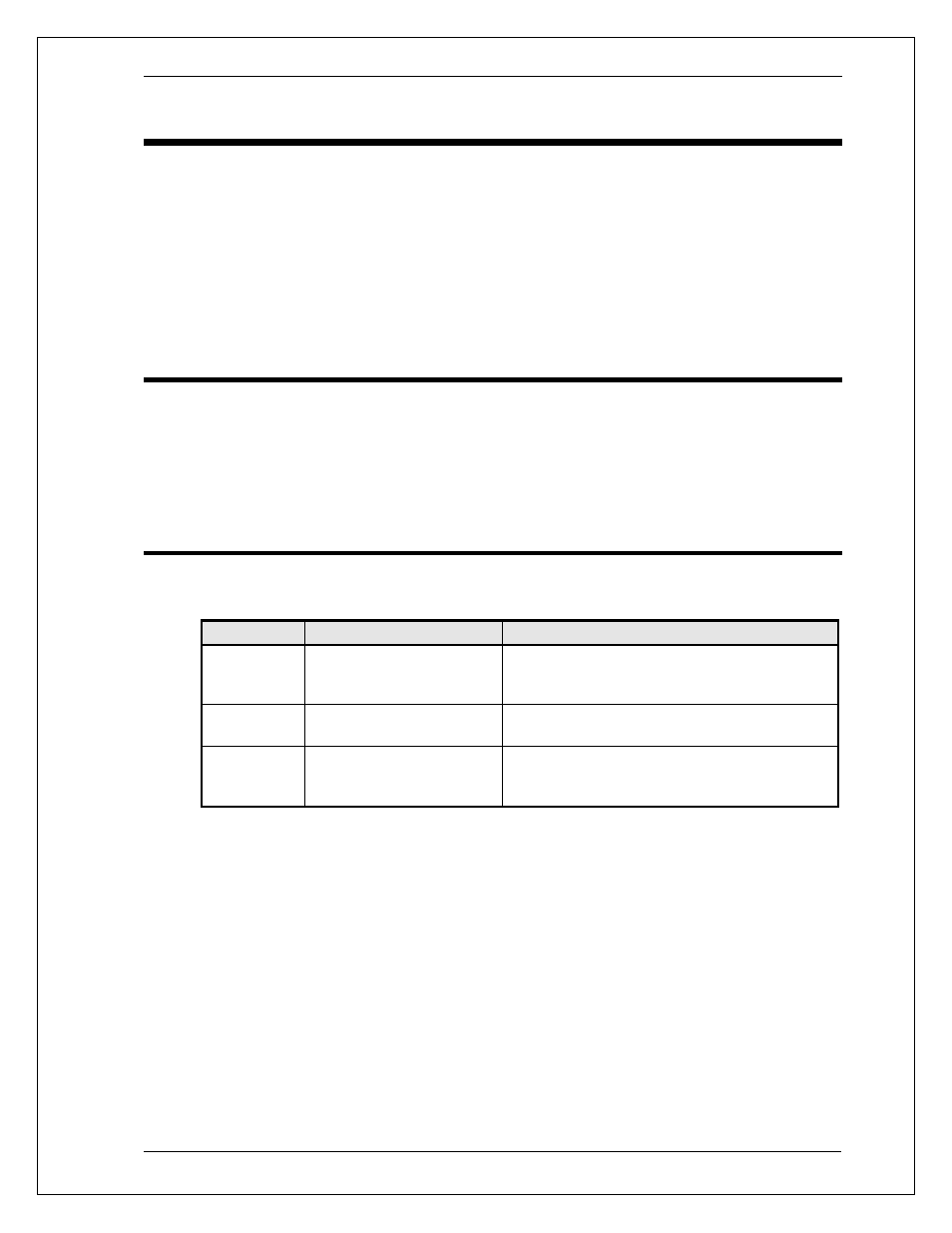

Register

Command

Description

Condition

STAT:OPER:COND?

A register that holds real-time status of the

circuits being monitored. It is a read-only

register.

Event

STAT:OPER:EVEN?

A register that latches any condition. It is a

read-only register that is cleared when read.

Enable

STAT:OPER:ENAB

A register that functions as a mask for

enabling specific bits from the Event register.

It is a read/write register.

Table 7-1: Operation Status Register

The outputs of the Operation Status register group are logically-ORed into the OPER(ation)

summary bit (7) of the Status Byte register.