Hardware considerations – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 91

I/O Model Reference

81

Hardware Considerations

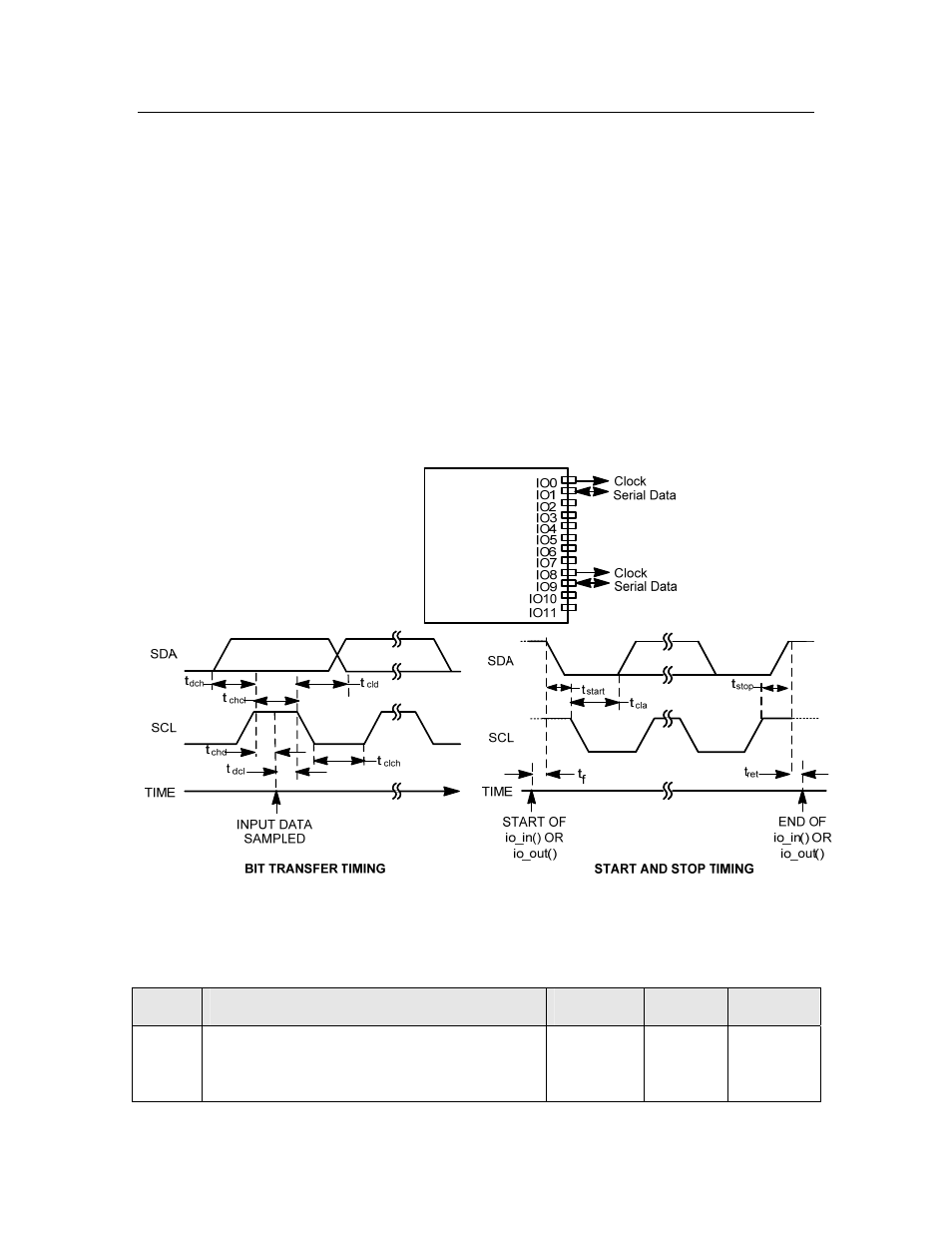

The Smart Transceiver is always the master, with IO8 as the serial clock (SCL)

signal and IO9 the serial data (SDA) signal. Alternatively, IO0 can be used as

the serial clock (SCL) and IO1 as the serial data (SDA). These I/O lines are

operated in the open-drain mode in order to accommodate the special

requirements of the I

2

C protocol. With the exception of two pull-up resistors, no

additional external components are necessary for interfacing a Smart

Transceiver to an I

2

C device.

Up to 255 bytes of data can be transferred at a time. At the start of all transfers,

a right-justified 7-bit I

2

C address argument is sent out on the bus immediately

after the I

2

C “start condition.” For more information about this protocol, refer to

UM10204: I

2

C-bus specification and user manual

from NXP Semiconductors.

Figure 29 shows the I

2

C I/O latency times. These are the times from the call to

the io_in() or io_out() function, until a value is returned. The direction of bit

ports can be changed between input and output dynamically by using the

io_set_direction() function.

Figure 29. I2C I/O and Timing

Table 32. I2C I/O Latency Values for Series 3100 Devices

Symbol Description

Minimum

Typical

Maximum

t

f

I/O call to start condition

io_in()

io_out()

—

54.6 μs

43.4 μs

—