Programming considerations, Figure 68 on – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 190

180

Timer/Counter Output Models

The actual active edge of the sync input and the triac gate output can be set by

using the clockedge or invert parameters, respectively.

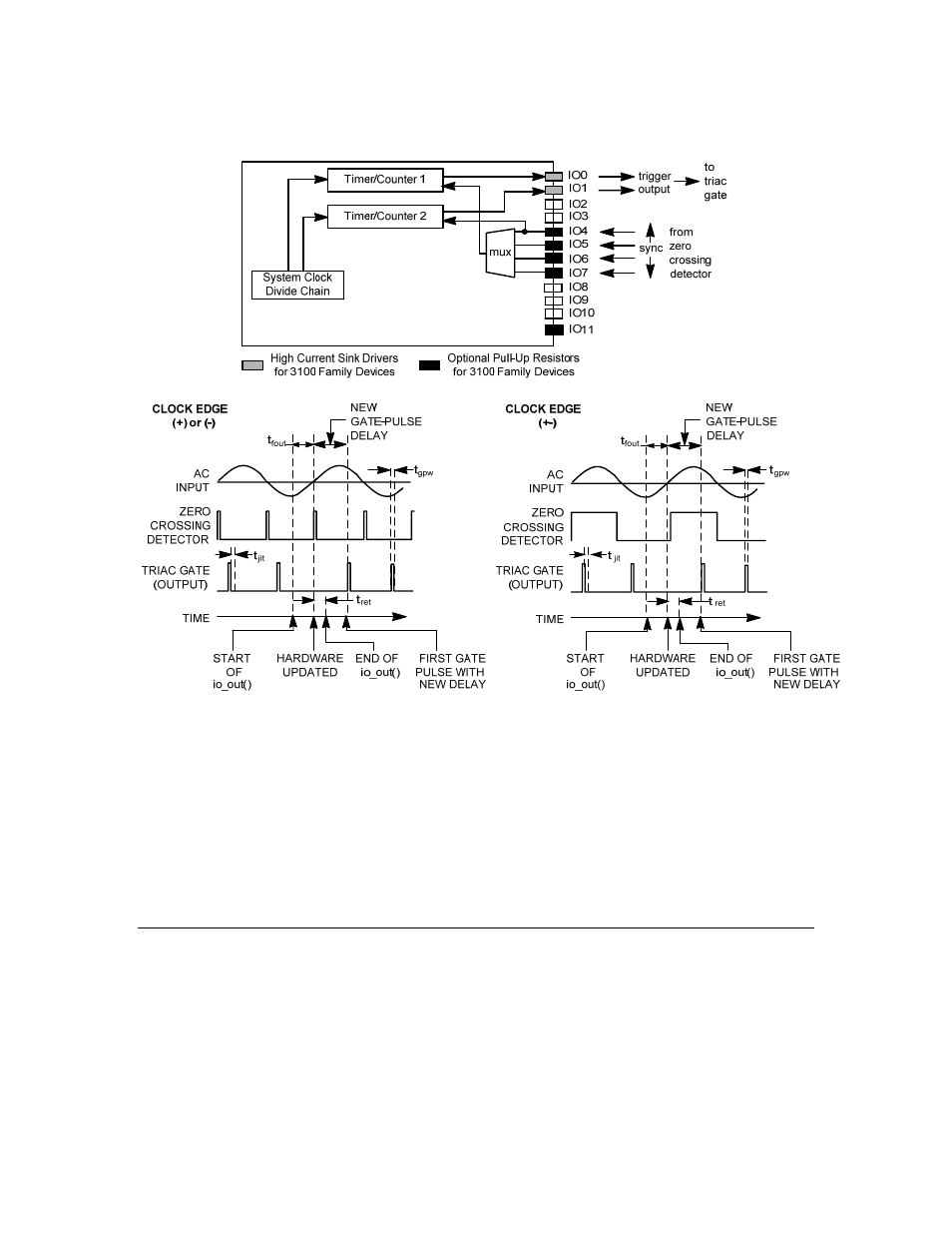

Figure 68. Triac Output and Timing

The hardware update does not happen until the occurrence of an external active

sync clock edge. The internal timer is then enabled, and a triac gate pulse is

generated after the user-defined period has elapsed. This sequence is repeated

indefinitely until another update is made to the triac gate pulse delay value.

t

fout

(min) refers to the delay from the initiation of the function call to the first

sampling of the sync input. In the absence of an active sync clock edge, the input

is repeatedly sampled for 10 ms (1/2 wave of a 50 Hz line cycle time), t

fout

(max),

during which the application processor is suspended.

Programming Considerations

Execution of this I/O model is synchronized with the sync pin input and might

not return for up to 10 ms. That is, the current application context could be

delayed for as long as 10 ms. Because of this synchronization, the frequency of

the sync pin input (and the frequency of the AC circuit being controlled) is

limited to the 50-60 Hz range.

When using the pulse output configuration, an output value of 65535 (the

overrange value) assures that no output pulse is generated. This is the