Programming considerations, Syntax – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 56

46

Direct I/O Models

Symbol Description

Minimum

Typical

Maximum

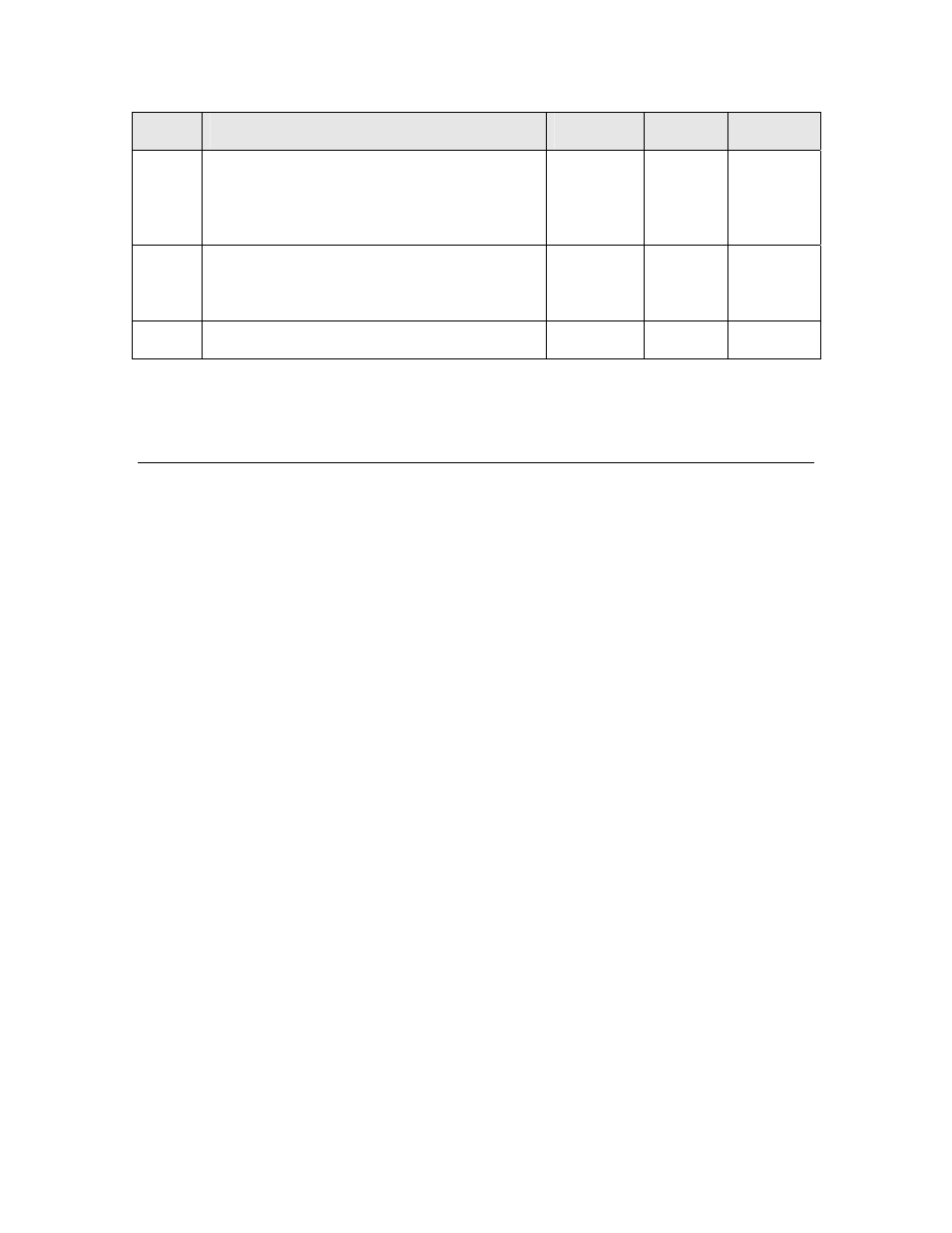

t

wrd

Start pulse edge to Smart Transceiver

releasing the data line

10 MHz

5 MHz

—

66.6 μs

72.0 μs

—

t

ibd

Inter-bit

delay

10 MHz

5 MHz

—

61.2 μs

122.4 μs

—

t

ret

Return from I/O call

—

42.6 μs —

The leveldetect input model can be used for detection of asynchronous

attachments of 1-Wire devices to the Smart Transceiver. In such a case, the

leveldetect input object is overlaid on top of the Touch I/O object. See

on page 17 for information about I/O object overlays.

Programming Considerations

The touch I/O model is used to interface to the 1-Wire protocol, and allows up to

255 bytes of data can be transferred at a time.

Syntax

pin

touch [output_pin(

pin

)] [timing(

t-low

,

t-rdi

,

t-wrd

)]

io-object-name

;

pin

An I/O pin. Touch I/O can specify one of the pins IO_0 through IO_7.

Multiple Touch I/O objects can be declared. If you do not explicitly declare a

separate output pin with the output_pin( ) parameter, this pin specifies both

the input and output pin. Otherwise, it specifies only the input pin.

output_pin(

pin

)

Optionally specifies the output pin. If not specified, the output pin is the

same as the input pin.

timing(…)

Optionally specifies three timing parameters. There are three time periods

associated with each bit time slot. All values here apply to a Series 3100

device with a 10 MHz input clock (and

double

for a 5 MHz input clock).

Because these timing controls affect the low-level single bit function used by

both read and write operations, they are required for both 1-wire read and

write operations. A value of 0 for a timing control is the same as a value of

256.

You can optionally specify the following three timing parameters when you

declare the touch I/O object:

•

t-low

The length of t

LOW

. This is the interval where the Neuron firmware

asserts a low on the 1-Wire bus signaling the start of the bit slot.