Dualslope input – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 135

I/O Model Reference

125

Important: The

first

measured value of a timer/counter is always discarded to

eliminate the possibility of a bad measurement after the chip comes out of a reset

condition.

Single events cannot be measured with the timer/counters

.

example of how the timer/counter objects are processed with a Neuron C when

statement.

TIME

INPUT

SIGNAL

STOP TIMER/COUNTER

SET FLAG LOAD NEW VALUE

INTO REGISTER

START

TIMER/

COUNTER

READ TIMER/COUNTER FLAG AND

REGISTER FROM THE PREVIOUS EVENT

END OF

io_in()

START OF

io_in()

STOP

TIMER/COUNTER

SET FLAG

LOAD EVENT

REGISTER

START

TIMER/

COUNTER

TIME

INPUT

SIGNAL

(event)

READ

TIMER/

COUNTER

FLAG AND

REGISTER

CLEAR FLAG

END OF

io_in()

START OF

io_in()

statement)

t

fin

t

ret

t

fin

t

ret

Example of a

when

statement

evaluating to true

(unless it is the

first event)

Example of a

when

statement

missing a current

event but

evaluating a

previous event

when

(

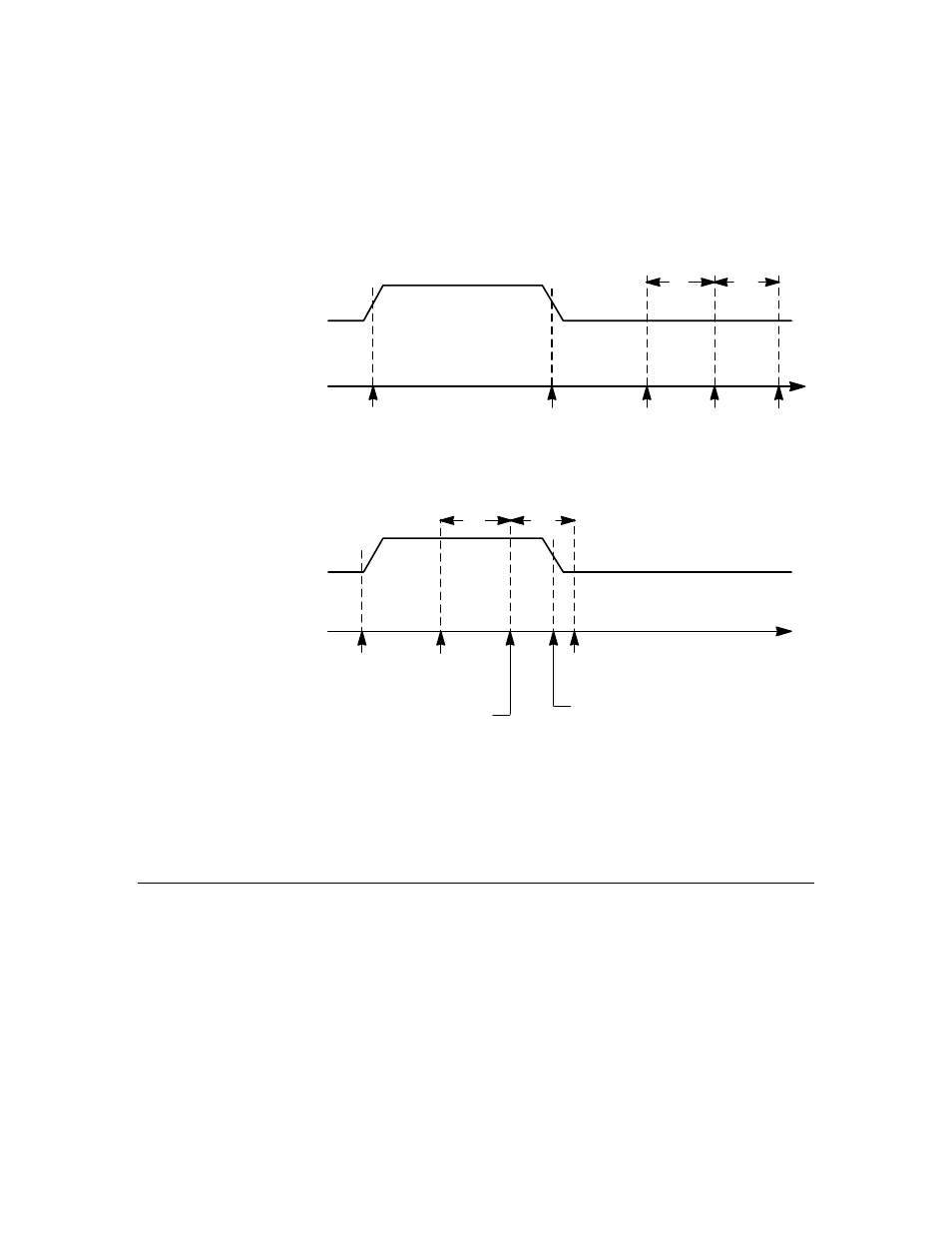

Figure 47. Example of when Statement Processing for the Ontime Input Object

As with all CMOS devices, floating I/O pins can cause excessive current

consumption. To avoid this excess current consumption, declare all unused I/O

pins as bit output. Alternatively, unused I/O pins can be connected to + VDD5

(for Series 3100 devices), +VDD33 (for Series 5000 devices), or GND.

Dualslope Input

The dualslope I/O model is used to control and measure the integration periods of

a dualslope integrating analog-to-digital (A/D) converter. You can use this I/O

model to implement low-cost A/D converters for analog input.

The I/O model controls a timer/counter output pin based on a control_value

argument and the state of a timer/counter input pin. When combined with

external analog circuitry, the Neuron Chip or Smart Transceiver performs A/D

measurements with 16 bits of resolution for as little as a 3.278 ms integration

period for a Series 3100 device with a 40 MHz input clock (the period scales with