Hardware considerations – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 194

184

Timer/Counter Output Models

This model applies to Series 3100 Neuron Chips and Smart Transceivers, and to

Series 5000 Neuron Processors and Smart Transceivers.

Hardware Considerations

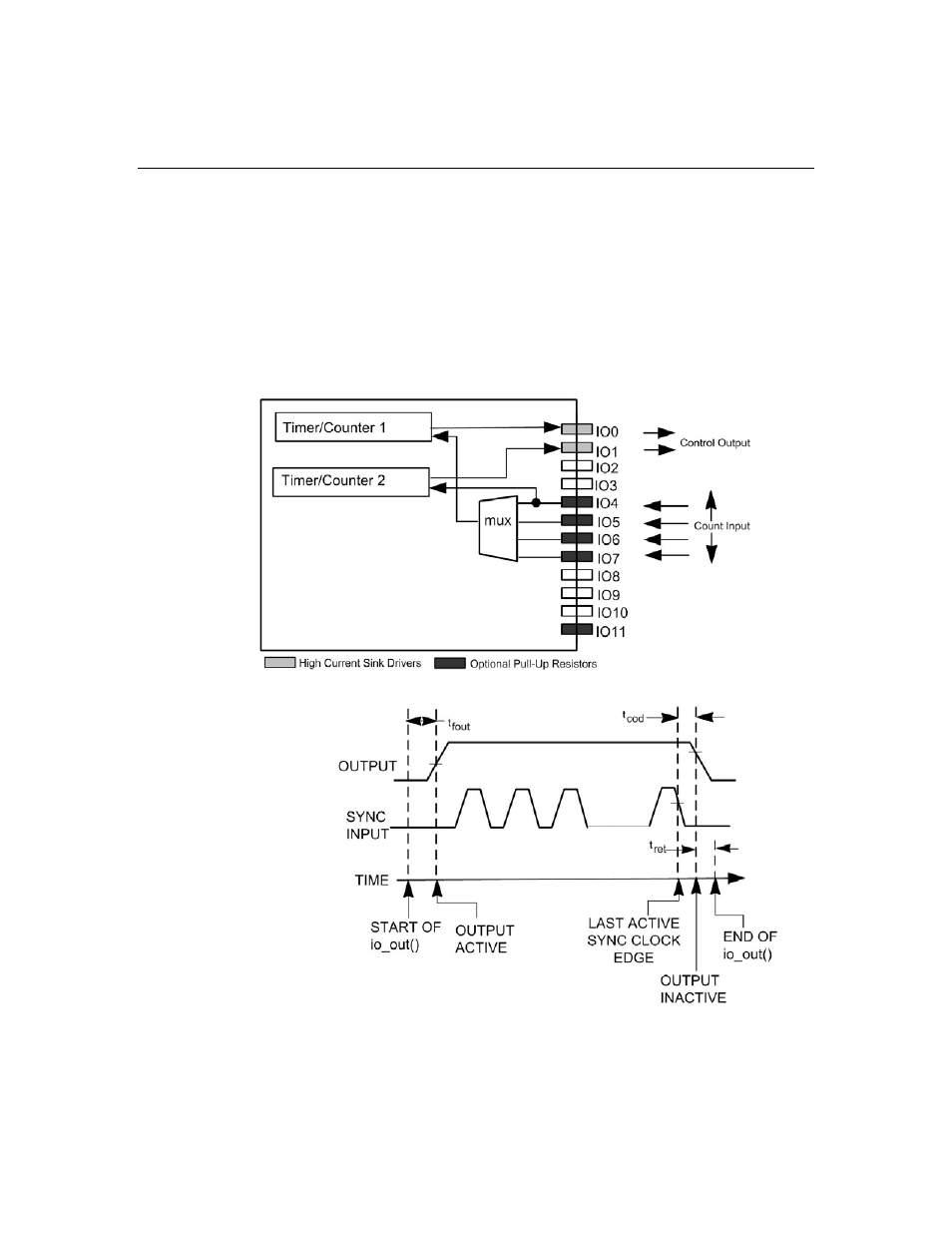

A timer/counter can be configured to generate an output pulse that is asserted

under program control, and de-asserted when a programmable number of input

edges (up to 65535) has been counted on an input pin (IO4 – IO7). Assertion can

be either logic high or logic low. This object is useful for controlling stepper

motors or positioning actuators which provide position feedback in the form of a

pulse train. The drive to the external device is enabled until it has moved the

required distance, and then the device is disabled (see Figure 71).

The active output level depends on whether the invert option is used in the

declaration of the function block. The default is high.

Figure 71. Triggered Count Output and Timing