Table 1, 4 throu – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 14

4

Introduction

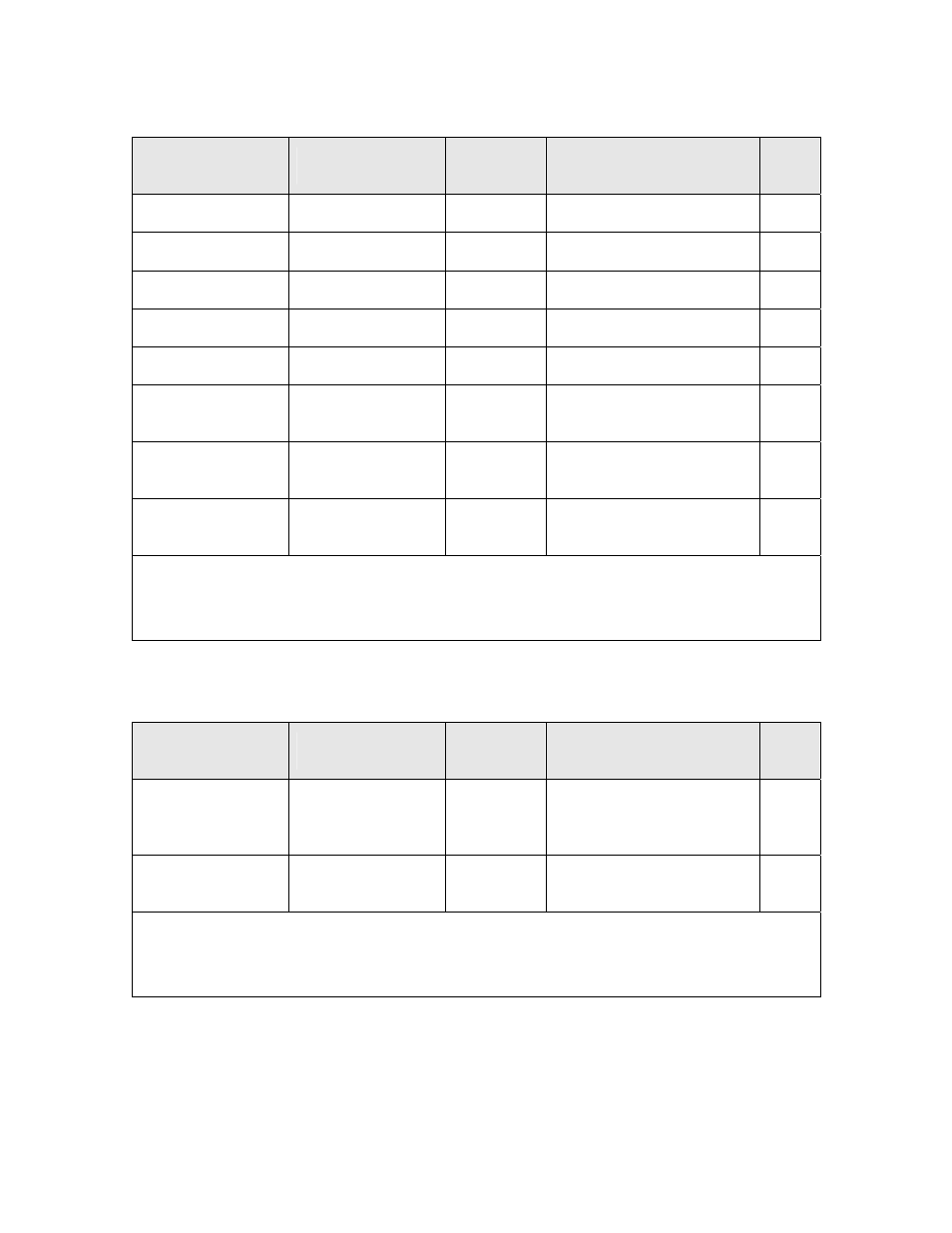

Table 1. Summary of the Direct I/O Models

I/O Model

Applicable I/O Pins Total Pins

per Object

Input/Output Value

Page

Bit Input

IO0 – IO11

1

0, 1 binary data

Bit Output

IO0 – IO11

1

0, 1 binary data

Byte Input

IO0 – IO7

8

0 – 255 binary data

Byte Output

IO0 – IO7

8

0 – 255 binary data

Leveldetect Input

IO0 – IO7

1

Logic 0 level detected

Nibble Input

Any adjacent four

in IO0 – IO7

4

0 – 15 binary data

Nibble Output

Any adjacent four

in IO0 – IO7

4

0 – 15 binary data

Touch I/O

IO0 – IO7

1

Up to 2048 bits of input or

output bits

Notes:

1. The IO11 pin for this I/O model is available only for the following device types: PL

3120-E4, PL 3150, PL 3170, FT 5000, and Neuron 5000.

See Chapter 2,

, on page 31, for more information about the

direct I/O models.

Table 2. Summary of the Parallel I/O Models

I/O Model

Applicable I/O Pins Total Pins

per Object

Input/Output Value

Page

Muxbus I/O

IO0 – IO10

11

Parallel bidirectional port

using multiplexed

addressing

Parallel I/O

IO0 – IO11

12

Parallel bidirectional

handshaking port

Notes:

1. The IO11 pin for this I/O model is available only for the following device types: FT

5000 and Neuron 5000.

See Chapter 3,

, on page 51, for more information about the

parallel I/O models.