Hardware considerations – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 20

10

Introduction

Example: The following I/O models can be combined for a Neuron Chip or Smart

Transceiver:

• 1 parallel I/O model (on IO_0..IO10)

OR

• 1 muxbus I/O model (on IO_0..IO10)

OR

• A combination of any or all of the other I/O models

A

through

E

shown in

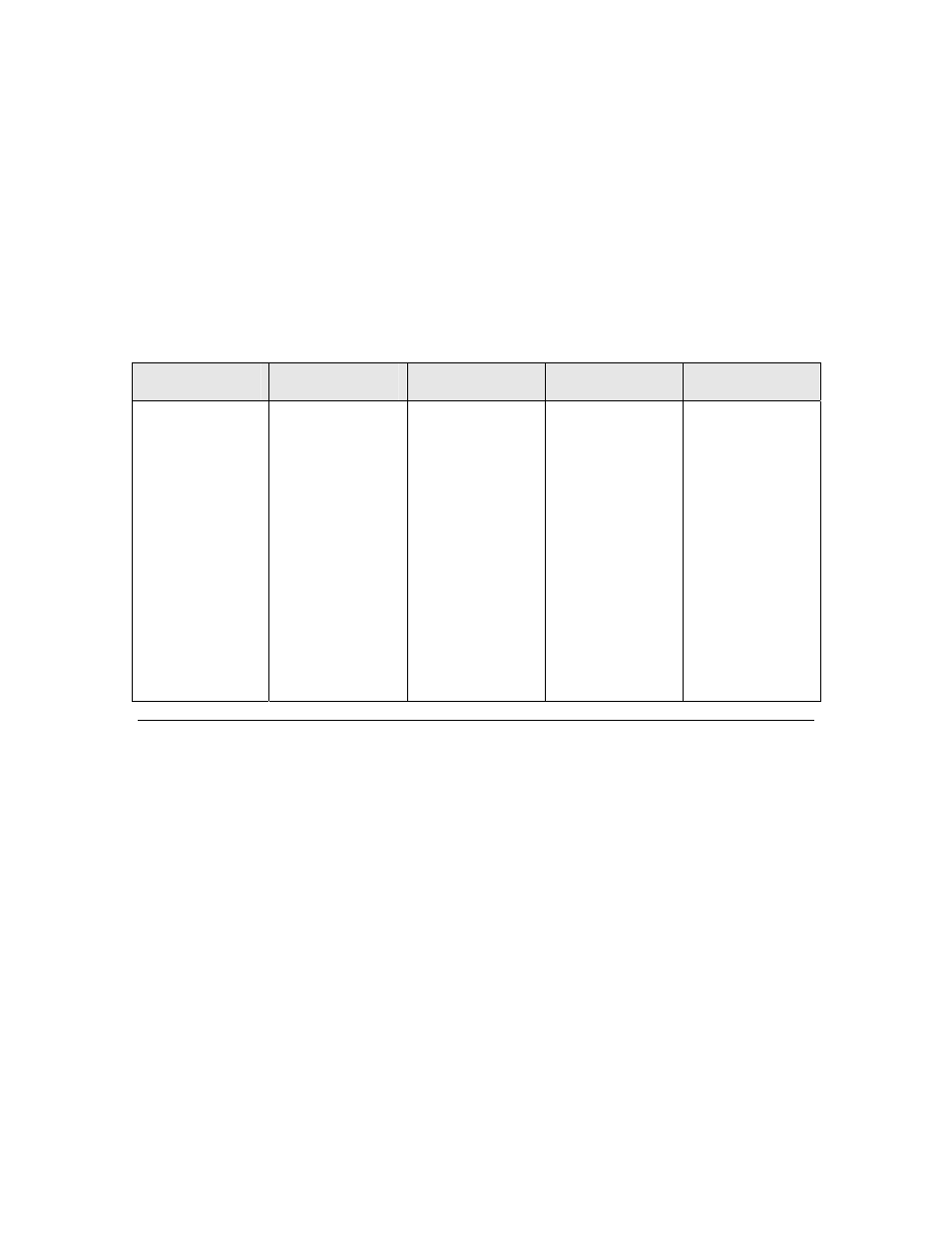

Table 6. Example I/O Model Combinations

A

B

C

D

E

1 to 4

timer/counter

inputs

(multiplexed on

IO_4, IO_5,

IO_6, IO_7),

including

quadrature

input on IO_6

1 timer/counter

input (on IO_4),

including

quadrature

input on IO_4

1 neurowire I/O

object (on IO_8,

IO_9, IO_10)

and 1 of IO_0 ...

IO_7

Any direct I/O

object type on

any pin (IO_0

through IO_10)

A bit I/O object

on IO_11

OR OR OR

1 timer/counter

output (on IO_0)

1 timer/counter

output (on IO_1)

1 serial I/O

object type (on

IO_8, IO_10)

Hardware Considerations

For a description of the electrical characteristics of the I/O pins, refer to

appropriate Series 3100 or Series 5000 device data sheet. Pins that are

configured as outputs can also be read as inputs, returning the value that was

last written to the pin. In addition, an application program can optionally specify

the initial values of digital outputs.

For Series 3100 devices, pins IO4 – IO7 and IO11 have optional pull-up current

sources that act as pull-up resistors. You use a Neuron C compiler directive

(#pragma enable_io_pullups) to enable these pull-ups. Also for Series 3100

devices, pins IO0 – IO3 have high current-sink capability (20 mA); the other pins

have standard current-sink capability.

For Series 3100 FT Smart Transceivers, the I/O pull-ups are enabled during the

stack initialization and built-in self-test (BIST) task (see the

FT 3120 / FT 3150

Smart Transceiver Data Book

for more information about the stack initialization

and BIST task). However, for Series 3100 PL Smart Transceivers, the I/O pull-

ups are not enabled during the stack initialization and BIST task.

Recommendation: For Series 3100 PL Smart Transceivers (especially for devices

with energy storage power supplies), you must ensure that I/O pins that are not