Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 118

108

Serial I/O Models

• In master mode, pin IO8 is the clock (driven by the Smart Transceiver),

IO9 is serial data input (Master In Slave Out or MISO), and IO10 is

serial data output (Master Out Slave In or MOSI).

• In slave mode, pin IO8 is the clock input, IO9 is serial data output

(MISO), and IO10 is serial data input (MOSI).

The declaration of the SPI I/O object supports several modifiers, including

neurowire. If the neurowire keyword is used, the pins assume a Neurowire-

compatible direction in which IO9 is always output and IO10 is always input.

Serial data is clocked out on the output pin at the same time as it is clocked in on

the input pin. In SPI master mode, no other masters are allowed on the bus. IO7

can be used as a select pin in slave mode, allowing the Smart Transceiver to

coexist with other slave mode devices on a 3-wire bus. A logic one level on the

select line disables the output drivers of the output pins and puts them in a high

impedance state.

If the Smart Transceiver is the only slave device on the SPI bus, and the master

device does not drive the Slave Select (SS~) signal (the signal is disabled), then

you can initialize the IO7 pin to a value of 1 and use it as an input pin:

• Pin IO7 should be declared as an input pin and externally grounded.

OR

• Pin IO7 must be declared in the following order:

IO_7 output bit io7out = 1; // initialize to '1'

IO_7 input bit io7in;

Note that SS~ should be used whenever possible to ensure proper

synchronization and recovery in the event of framing errors from the master

device.

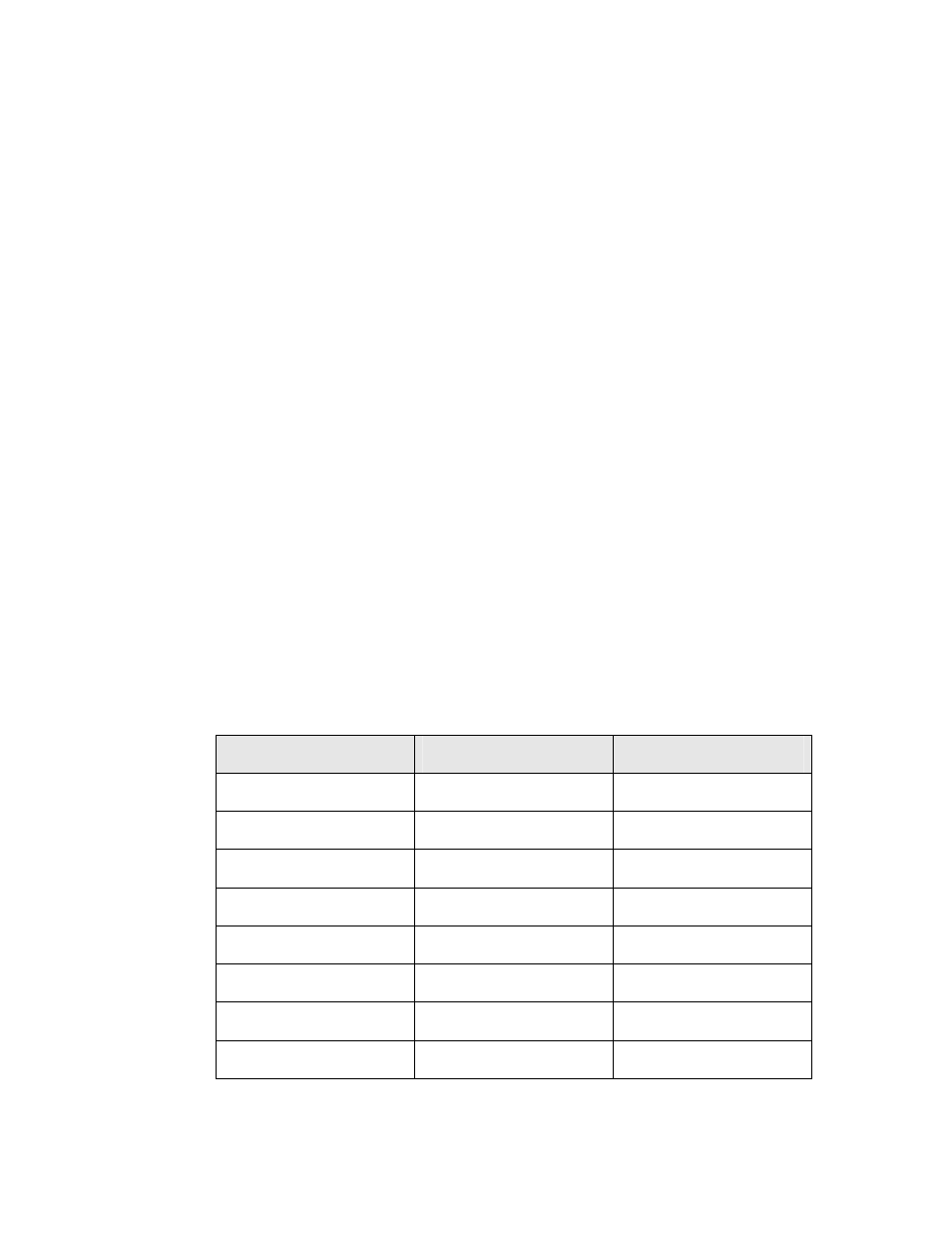

The bit rates supported by the SPI port are summarized in Table 39 through

Table 39. SPI Master Mode for Series 3100 Power Line Devices

Clock

Bit Rate for 10 MHz

Bit Rate for 6.5536 MHz

7

19.531 kbps

12.8 kbps

6

39.063 kbps

25.6 kbps

5

78.125 kbps

51.2 kbps

4

156.250 kbps

102.4 kbps

3

312.500 kbps

204.8 kbps

2

625.000 kbps

409.6 kbps

1

1250.000 kbps

819.2 kbps

0

2500.000 kbps

1638.4 kbps