Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 74

64

Parallel I/O Models

IO10 = 1

IO10 = 0

R/W~ = 1

IO10 = 1

READ ONLY

STATUS REGISTER

READ/WRITE

DATA REGISTER

D0/HS

IO10

IO9

IO8

IO0

IO1

IO2

IO3

IO4

IO5

IO6

IO7

A0

R/W~

CS~

HS

SLAVE B

D7

D6

D5

D4

D3

D2

D1

HS/D0 – D7

X

X

X

X

X

X

X

D0

D1

D2

D3

D4

D5

D6

D7

OR

IO11

R/W~ = 1

R/W~ = 0 OR 1

IRQ

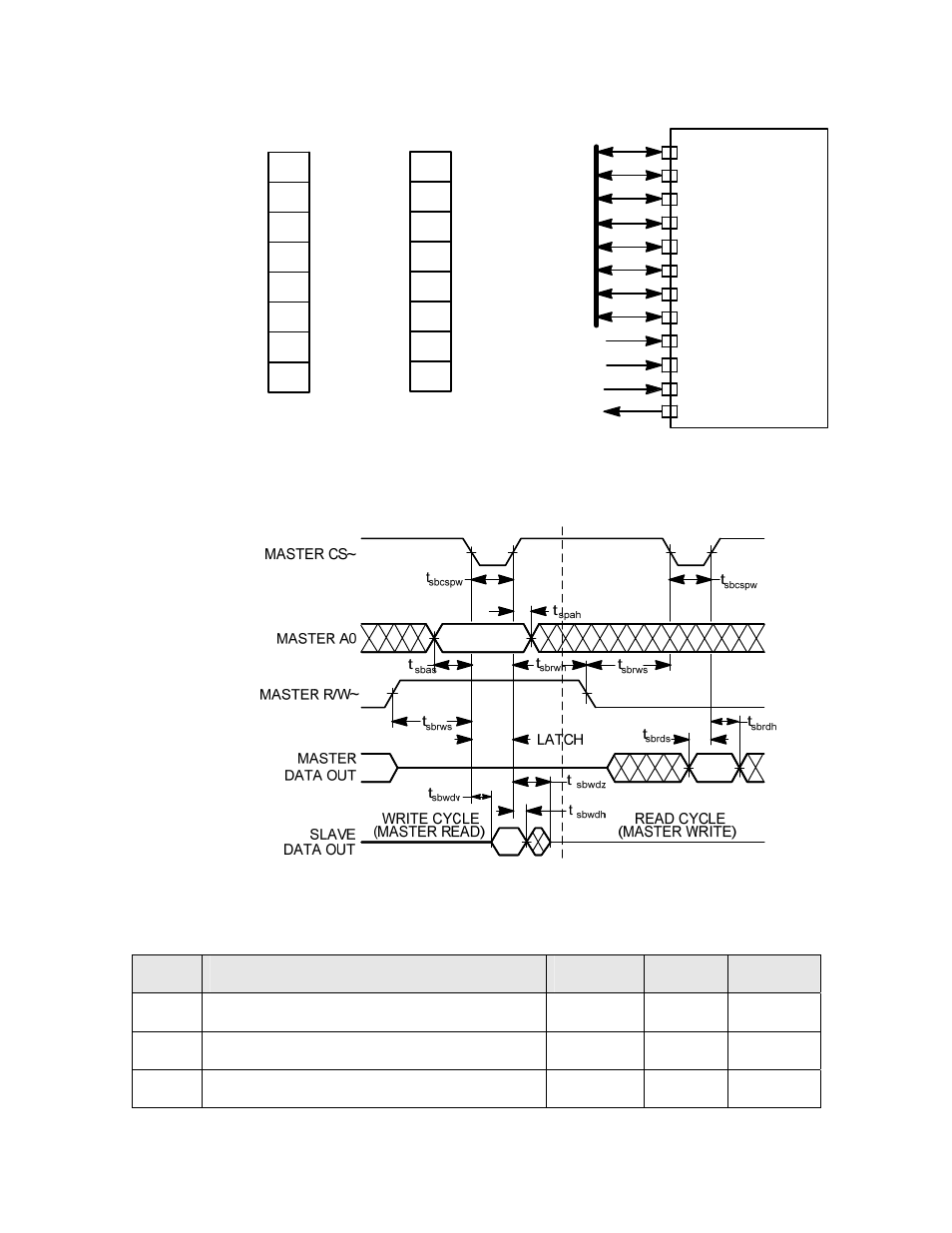

Figure 22. Parallel I/O Master/Slave B as a Memory-Mapped Device

Figure 23. Slave B Mode Timing

Table 23. Slave B Mode Parallel I/O Latency Values for Series 3100 Devices

Symbol Description

Minimum

Typical

Maximum

t

sbrws

R/W~ setup before falling edge of CS~

0 ns

—

—

t

sbrwh

R/W~ hold after rising edge of CS~

0 ns

—

—

t

sbcspw

CS~ pulse width

Note 1

—

—