Table 71 on, 194 lists the p, Table 71 – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 204

194

Timer/Counter Periods and Resolution

If you specify an alternate clock value (using the io_set_clock() function with a

TCCLK_* macro value) that is lower than your device’s system clock setting, the

resolution and range values reflect the expected values specified in Table 71.

However, you cannot specify a value that defines a clock rate that is higher than

one-half of the device’s system clock. For example, if your system clock rate is 20

MHz, you can specify any TCCLK_* macro that defines a 10 MHz or lower clock

rate (that is, you cannot specify TCCLK_40MHz or TCCLK_20MHz – no error is

issued, but the effective value used in this case is TCCLK_10MHz).

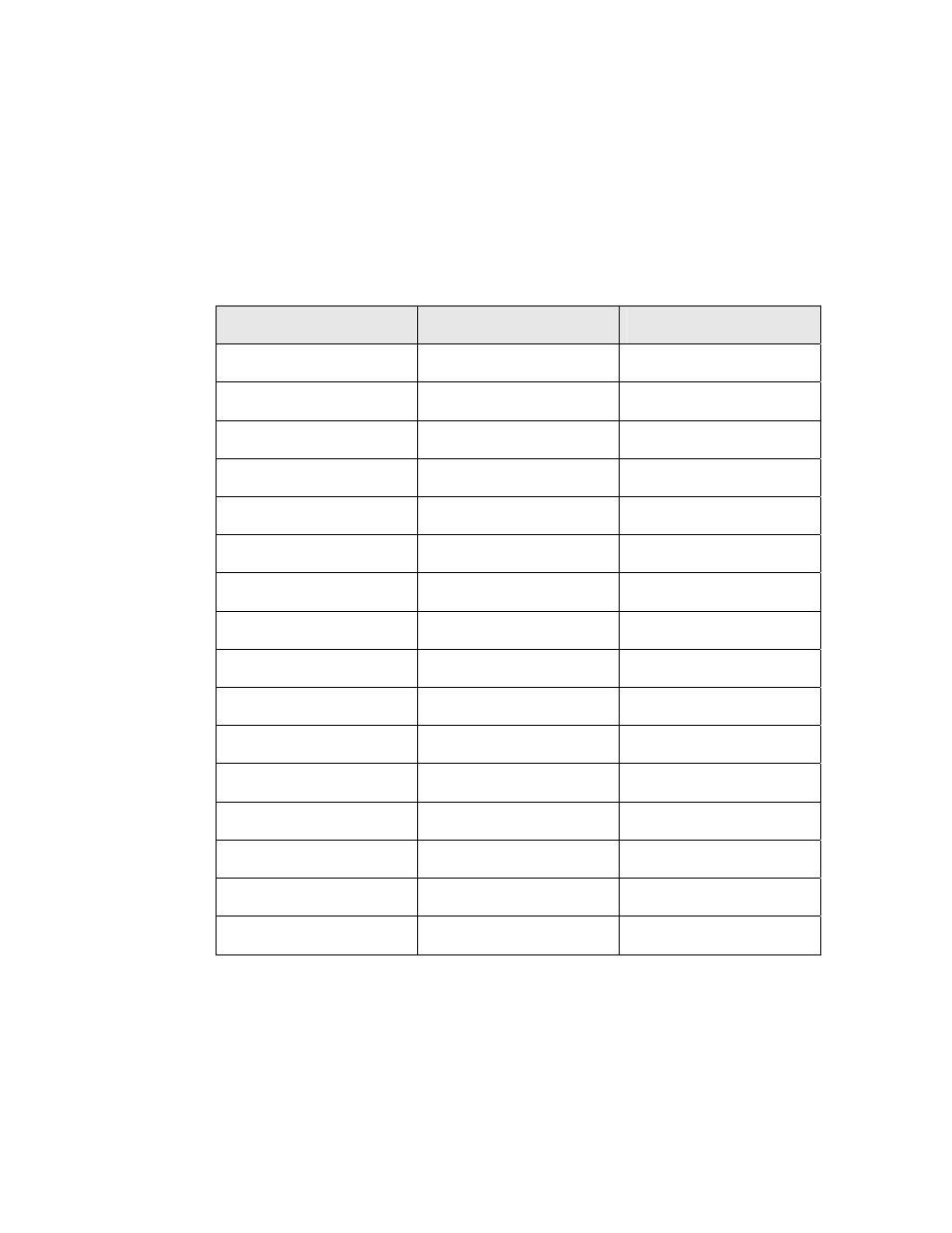

Table 71. Series 5000 Timer/Counter Pulsetrain Output

TCCLK Macro

Frequency

Period

TCCLK_40MHz

610.4 Hz

1.64 ms

TCCLK_20MHz

305.2 Hz

3.28 ms

TCCLK_10MHz

152.6 Hz

6.56 ms

TCCLK_5MHz

76.3 Hz

13.1 ms

TCCLK_2500kHz

38.1 Hz

26.2 ms

TCCLK_1250kHz

19.1 Hz

52.4 ms

TCCLK_625kHz

9.54 Hz

105 ms

TCCLK_312k5Hz

4.77 Hz

210 ms

TCCLK_156k2Hz

2.38 Hz

419 ms

TCCLK_78k12Hz

1.19 Hz

839 ms

TCCLK_39k06Hz

0.60 Hz

1678 ms

TCCLK_19k53Hz

0.30 Hz

3.4 sec

TCCLK_9k77Hz

0.15 Hz

6.7 sec

TCCLK_4k88Hz

0.075 Hz

13.4 sec

TCCLK_2k44Hz

0.037 Hz

26.8 sec

TCCLK_1k22Hz

0.019 Hz

53.7 sec