Table 21 on, 58), refers t – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 68

58

Parallel I/O Models

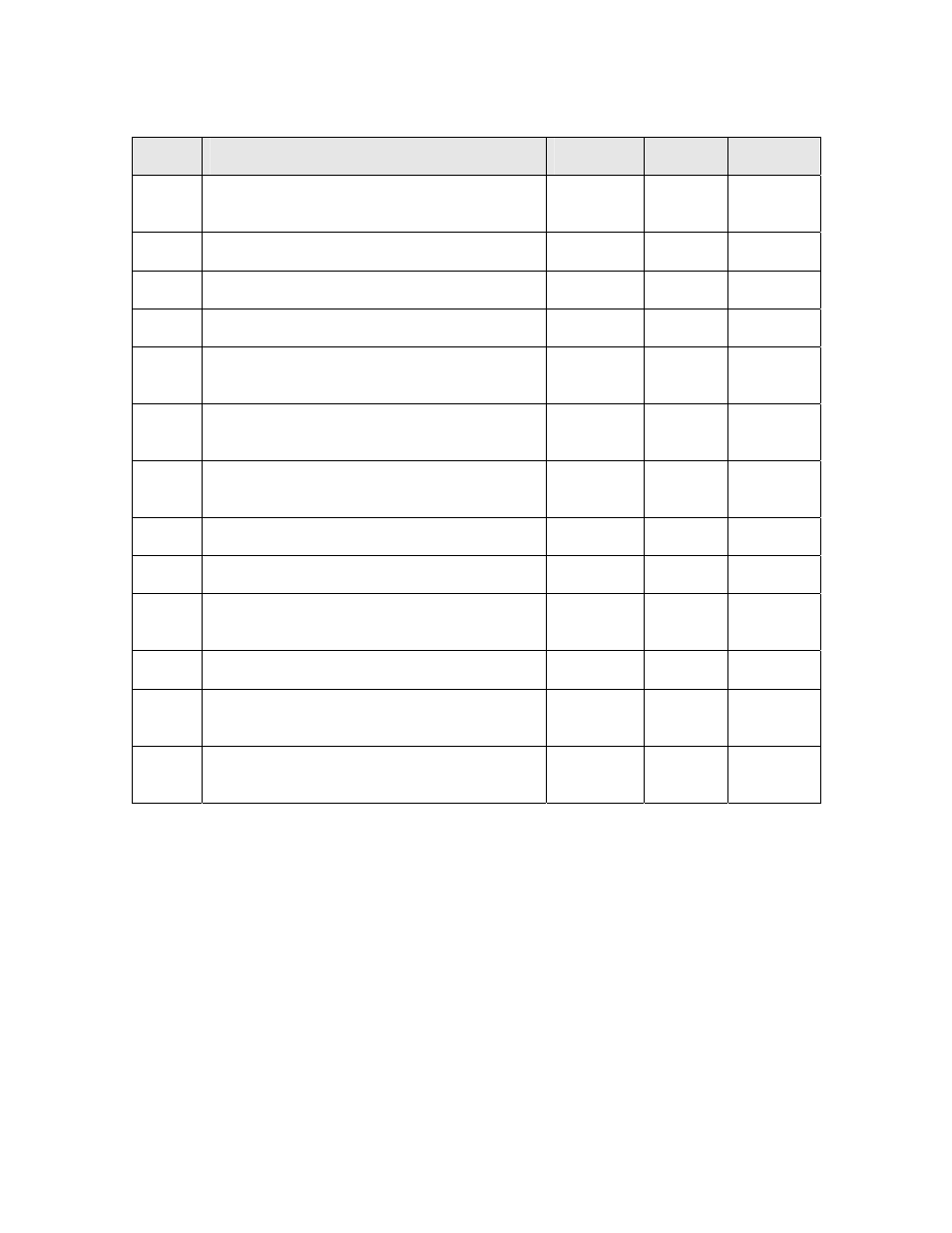

Table 21. Master Mode Parallel I/O Latency Values for Series 3100 Devices

Symbol Description

Minimum

Typical

Maximum

t

mrws

R/W~ setup before falling edge of CS~ (See

note 1)

150 ns

3 XIN

—

t

mrwh

R/W~ hold after rising edge of CS~

100 ns

—

—

t

mcspw

CS~ pulse width (See note 1)

150 ns

2 XIN

—

t

mhsh

HS hold after falling edge of CS~

0 ns

—

—

t

mhsv

HS checked by firmware after rising edge of

CS~ (See note 1)

150 ns

10 XIN

—

t

mrdz

Master three-state DATA after rising edge of

R/W~ (See notes 2, 3)

—

0 ns

25 ns

t

mrds

Read data setup before falling edge of HS

(See note 4)

0 ns

—

—

t

mhscs

HS low to falling edge of CS~ (See notes 5, 1) 2 XIN

6 XIN

—

t

mrdh

Read data hold after falling edge of CS~

0 ns

—

—

t

mwdd

Master drive of DATA after falling edge of

R/W~ (See notes 2, 1)

150 ns

2 XIN

—

t

mhsdv

HS low to data valid (See note 5)

—

50 ns

—

t

mwds

Write data setup before rising edge of CS~

(See note 1)

150 ns

2 XIN

—

t

mwdh

Write data hold after rising edge of CS~ (See

note 6)

Note 6

—

—