Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 119

I/O Model Reference

109

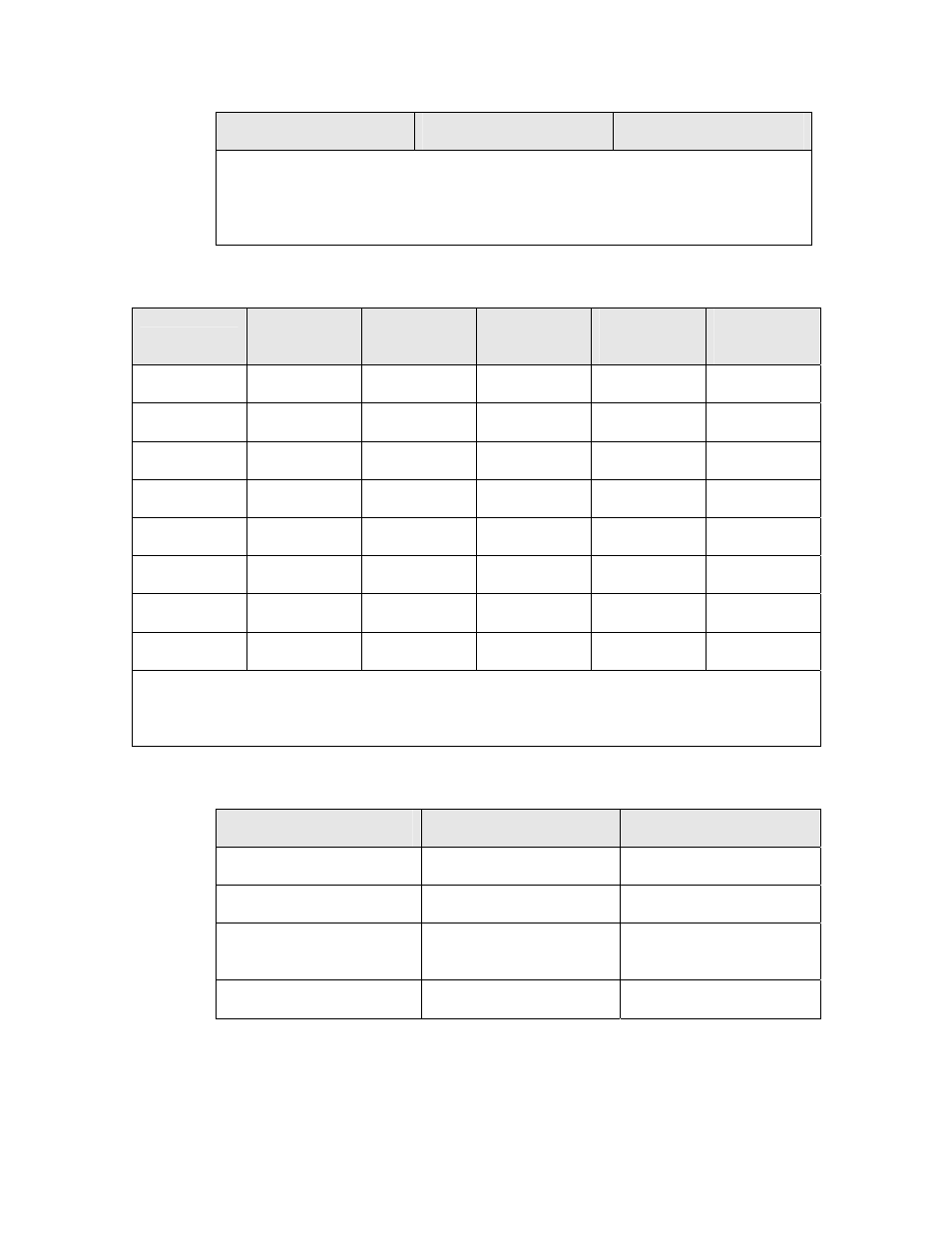

Clock

Bit Rate for 10 MHz

Bit Rate for 6.5536 MHz

Note: For Clock 5 and higher bit rates, the bit rate shown is the peak rate. The

data is burst out in pairs of bytes, and the overall average data rate is limited to

approximately 40 kbps and 25 kbps for 10 MHz and 6.5536 MHz input clocks,

respectively.

Table 40. SPI Master Mode for Series 5000 Devices

Clock

Bit Rate for

80 MHz

Bit Rate for

40 MHz

Bit Rate for

20 MHz

Bit Rate for

10 MHz

Bit Rate for

5 MHz

7

156.25 kbps

78.125 kbps

39.063 kbps

19.531 kbps

9.765 kbps

6

312.5 kbps

156.25 kbps

78.125 kbps

39.063 kbps

19.531 kbps

5

625 kbps

312.5 kbps

156.25 kbps

78.125 kbps

39.063 kbps

4

1.25 Mbps

625 kbps

312.5 kbps

156.25 kbps

78.125 kbps

3

2.5 Mbps

1.25 Mbps

625 kbps

312.5 kbps

156.25 kbps

2

5 Mbps

2.5 Mbps

1.25 Mbps

625 kbps

312.5 kbps

1

10 Mbps

5 Mbps

2.5 Mbps

1.25 Mbps

625 kbps

0

20 Mbps

10 Mbps

5 Mbps

2.5 Mbps

1.25 Mbps

Note: For Clock 5 and higher bit rates, the bit rate shown is the peak rate. The data is burst

out in pairs of bytes, and the overall average data rate is limited to approximately 430 kbps

for an 80 MHz system clock.

Table 41. SPI Slave Mode for Series 3100 Power Line Devices

Parameter

Value for 10 MHz

Value for 6.5536 MHz

Max burst rate

1250 kbps

819.2 kbps

Max burst size

2 bytes

2 bytes

Min burst spacing (from

start of one burst to next)

400 μs 640

μs

Max sustained data rate

40 kbps

25 kbps