Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 17

I/O Model Reference

7

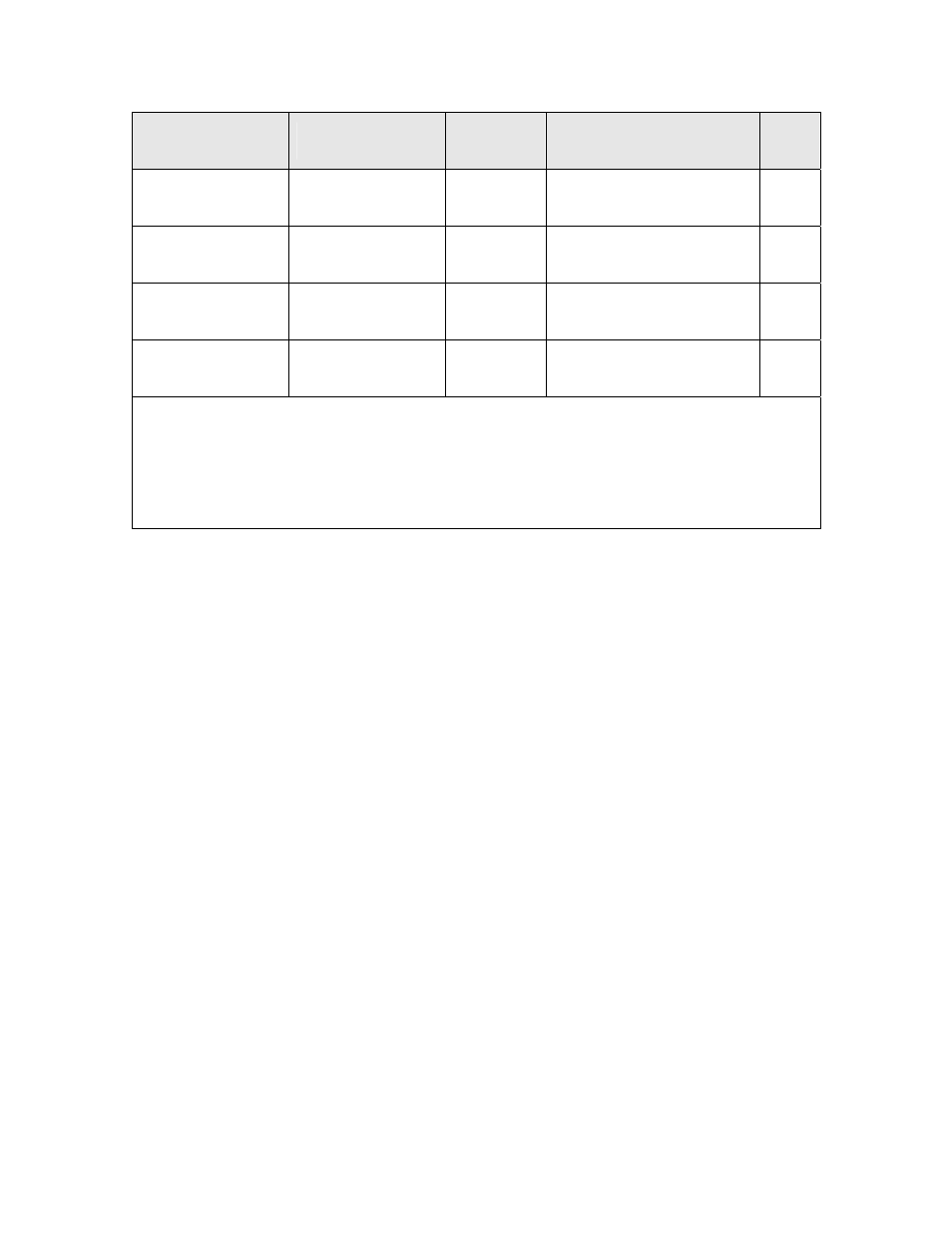

I/O Model

Applicable I/O Pins Total Pins

per Object

Input/Output Value

Page

Pulsewidth Output IO0, IO1

1

0 – 100% duty cycle pulse

train

Stretched Triac

Output

IO0, IO1 + (one of

IO4 – IO7)

2

Delay of output pulse with

respect to input edge

Triac Output

IO0, IO1 + (one of

IO4 – IO7)

2

Delay of output pulse with

respect to input edge

Triggered-

Count Output

IO0, IO1 + (one of

IO4 – IO7)

2

Output pulse controlled by

counting input edges

Notes:

1. The Stretched Triac Output model is available only for the following device types: FT

5000 and Neuron 5000.

2. Dual-edge triggering is not available for the following device types: Neuron 3150, FT

3150, or PL 3150.

See Chapter 6,

, on page 155, for more information

about the timer/counter output models.

Neuron Chips and Smart Transceivers have two 16-bit timer/counters on-chip.

The input to timer/counter 1, also called the

multiplexed timer/counter,

is

selectable among pins IO4 – IO7, through a programmable multiplexer and its

output can be connected to pin IO0. The input to timer/counter 2, also called the

dedicated timer/counter,

can be connected to pin IO4 and its output to pin IO1.

The timer/counters are implemented as a 16-bit load register writable by the

CPU, a 16-bit counter, and a 16-bit latch readable by the CPU. The load register

and latch are accessed a byte at a time. No I/O pins are dedicated to

timer/counter functions. If, for example, timer/counter 1 is used for input signals

only, then IO0 is available for other input or output functions. Timer/counter

clock and enable inputs can be from external pins, or from scaled clocks derived

from the system clock; the clock rates of the two timer/counters are independent

of each other. External clock actions occur optionally on the rising edge, the

falling edge, or both rising and falling edges of the input.

For Series 5000 devices, many of the timer/counter I/O models can also trigger

interrupt tasks, which can provide minimum application latency for I/O events

that are related to the timer/counter models. See the

Neuron C Programmer’s

Guide

for more information about defining and using interrupts for Series 5000

devices.

Multiple timer/counter input objects can be declared on different pins within a

single application. By calling the io_select()

function, the application can use the

first timer/counter to implement up to four different input objects. If a

timer/counter is configured to implement one of the output models, or is

configured as a quadrature input object, then it can not be reassigned to another

timer/counter object in the same application program.