Series 5000 square wave output – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 202

192

Timer/Counter Periods and Resolution

Series 5000 Square Wave Output

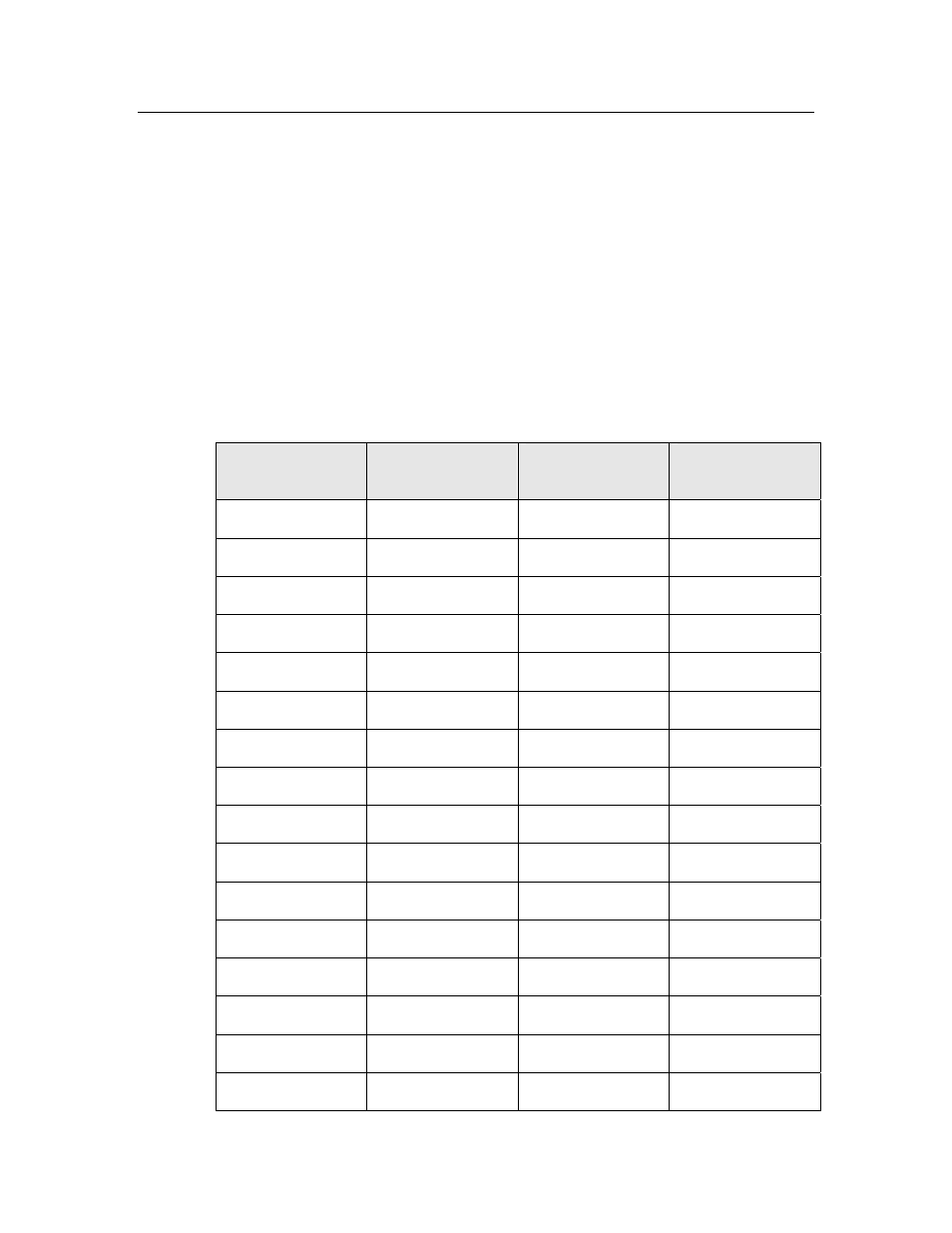

For pulsewidth short output and pulsecount output, Table 69 lists the possible

choices for pulsetrain repetition frequencies for a Series 5000 device.

The resolution and range values in Table 69 apply to all system clock settings,

that is, they do not scale with changes to the system clock.

If you specify an alternate clock value (using the io_set_clock() function with a

TCCLK_* macro value) that is lower than your device’s system clock setting, the

resolution and range values reflect the expected values specified in Table 69.

However, you cannot specify a value that defines a clock rate that is higher than

one-half of the device’s system clock. For example, if your system clock rate is 20

MHz, you can specify any TCCLK_* macro that defines a 10 MHz or lower clock

rate (that is, you cannot specify TCCLK_40MHz or TCCLK_20MHz – no error is

issued, but the effective value used in this case is TCCLK_10MHz).

Table 69. Series 5000 Timer/Counter Square Wave Output

TCCLK Macro

Repetition Rate

Repetition Period

or Pulse Period

Resolution of

Pulse

TCCLK_40MHz 156.2

kHz

6.4

μs 25

ns

TCCLK_20MHz 78.1

kHz

12.8

μs 50

ns

TCCLK_10MHz 39.1

kHz

25.6

μs 0.1

μs

TCCLK_5MHz 19531

Hz

51.2

μs 0.2

μs

TCCLK_2500kHz 9766

Hz

102.4

μs 0.4

μs

TCCLK_1250kHz 4883

Hz

204.8

μs 0.8

μs

TCCLK_625kHz 2441

Hz

409.6

μs 1.6

μs

TCCLK_312k5Hz 1221

Hz

819.2

μs 3.2

μs

TCCLK_156k2Hz 610

Hz

1638.4

μs 6.4

μs

TCCLK_78k12Hz 305

Hz

3276.8

μs 12.8

μs

TCCLK_39k06Hz 153

Hz

6553.6

μs 25.6

μs

TCCLK_19k53Hz

76.3 Hz

13.11 ms

51.2 μs

TCCLK_9k77Hz

38.1 Hz

26.21 ms

102.4 μs

TCCLK_4k88Hz

19.1 Hz

52.43 ms

204.8 μs

TCCLK_2k44Hz

9.5 Hz

104.86 ms

409.6 μs

TCCLK_1k22Hz

4.77 Hz

209.72 ms

819.2 μs