Hardware considerations – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 149

I/O Model Reference

139

time_on (ns) = return_value * 2000 * 2^(value) / 10 MHz

where value ranges from 0..15

You can use this model to implement digital-to-analog (D/A) converters,

frequency counters, or tachometers.

This model applies to Series 3100 Neuron Chips and Smart Transceivers, and to

Series 5000 Neuron Processors and Smart Transceivers.

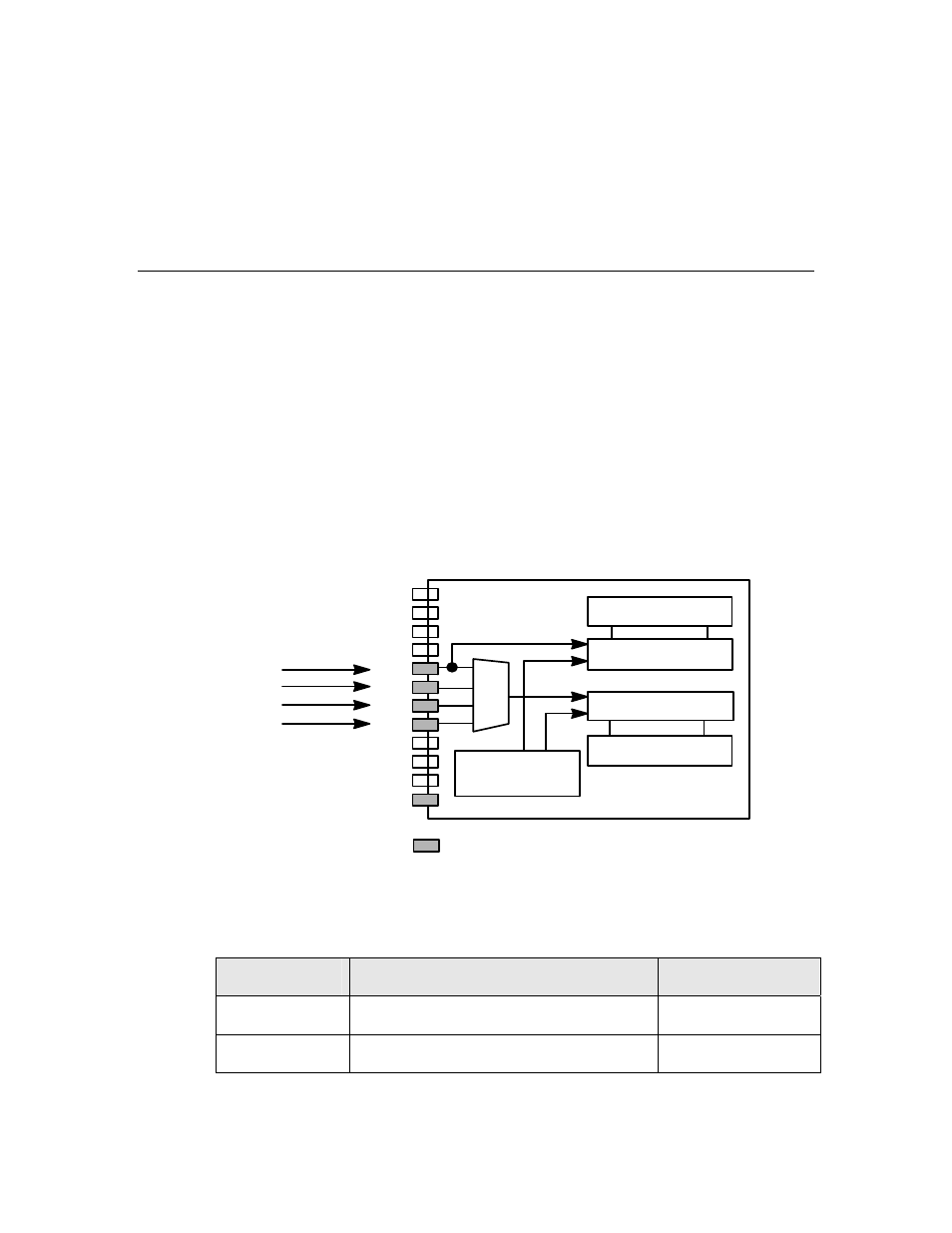

Hardware Considerations

A timer/counter can be configured to measure the time for which its input is

asserted. The resolution and range of the timer/counter period options is

described in

Timer/Counter Resolution and Maximum Range

on page 188.

Assertion can be defined as either logic high or logic low. This model can be used

as a simple analog-to-digital converter with a voltage-to-time circuit, or for

measuring velocity by timing motion past a position sensor (see Figure 47 on

The ontime I/O model is level sensitive. The active level of the input signal gates

the clock driving the internal counter in the Neuron Chip or Smart Transceiver.

The actual active level of the input depends on whether the invert option is used

in the declaration of the I/O object. The default is the high level.

mux

Event Register

IO10

IO9

IO8

IO0

IO1

IO2

IO3

IO4

IO5

IO6

IO7

System Clock

Divide Chain

Optional Pull-Up Resistors for 3100 Family Devices

Event Register

Timer/Counter 2

Timer/Counter 1

IO11

Figure 52. Ontime Input

Table 53. Ontime Input Latency Values for Series 3100 Devices

Symbol

Description

Typical at 10 MHz

t

fin

Function call to input sample

86 μs

t

ret

Return from function

52 μs or 22 μs