I/o timing issues – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 22

12

Introduction

For Series 5000 devices, the sample rate is equivalent to the system clock rate.

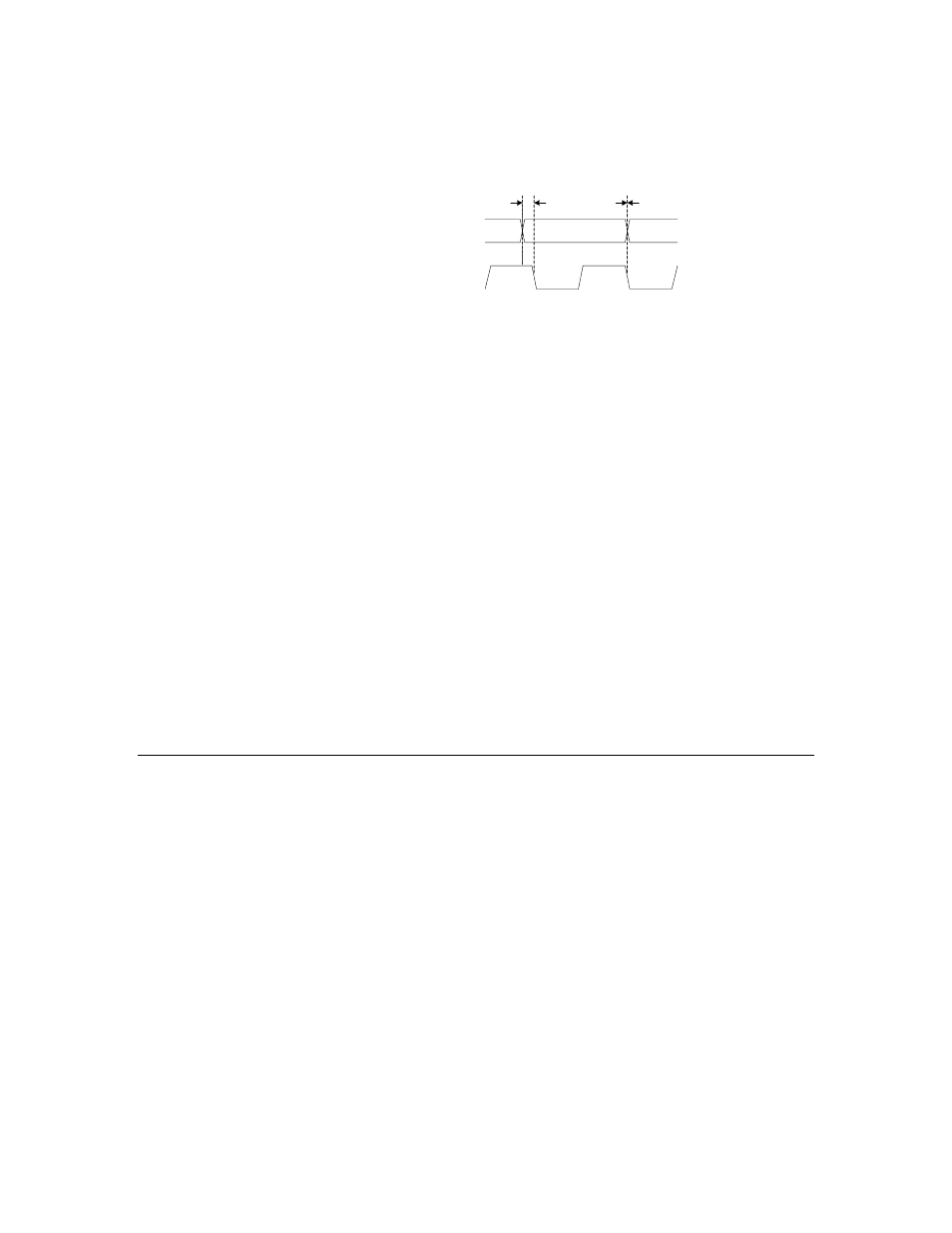

For a signal to be reliably synchronized with an 80 MHz system clock, it must be

at least 17.5 ns in duration; see Figure 4.

80 MHz

System Clock

IO0-IO11 Inputs

(17.5 ns pulse)

t

setup

5 ns

t

hold

0 ns

Figure 4. Synchronization of External Signals for Series 5000 Devices

Any event that lasts longer than 220 ns (for a Series 3100 device at 10 MHz) or

17.5 ns (for a Series 5000 device at 80 MHz) is synchronized by hardware, but

there can be latency in software sampling, which can result in a delay in

detecting the event. If the state changes at a faster rate than software sampling

can process, the interim changes are not detected.

The following exceptions apply to the use of the synchronization block:

• The chip select (CS~) input used in the slave B mode of the parallel I/O

object recognizes rising edges asynchronously.

• The leveldetect input is latched by a flip-flop with a 200 ns clock (for

Series 3100 devices) or a 12.5 ns clock (for Series 5000 devices). The level

detect transition event is latched, but there is a delay in software

detection.

• The SCI (UART) and SPI objects are buffered on byte boundaries by the

hardware, and are transferred to memory using an interrupt.

• Events on the I/O pins for the input timer/counter functions are

accurately measured, and a value returned to a register, regardless of the

state of the application or interrupt processor within the Neuron Chip or

Smart Transceiver. However, the application processor can be delayed in

reading the register.

I/O Timing Issues

The I/O timing for Neuron Chips and Smart Transceivers is influenced by four

separate, yet overlapping, areas of the overall chip architecture:

• The scheduler

• The I/O model’s firmware

• The Neuron Chip or Smart Transceiver hardware

• Interrupts

The contribution of the scheduler to the overall I/O timing is approximately

uniform across all I/O objects because its contribution to the overall I/O timing is

at a relatively high functional level.

The contribution of both firmware and hardware varies from one I/O model to

another (for example, Bit I/O as opposed to Neurowire I/O).

The contribution of interrupts varies with the nature of the data interrupting the

processor. See

on page 98 and

on