Figure 8, 33 an, 33 sh – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 43

I/O Model Reference

33

TIME

INPUT PIN

SAMPLED

END OF

io_in()

START OF

io_in()

INPUT

t

fin

t

ret

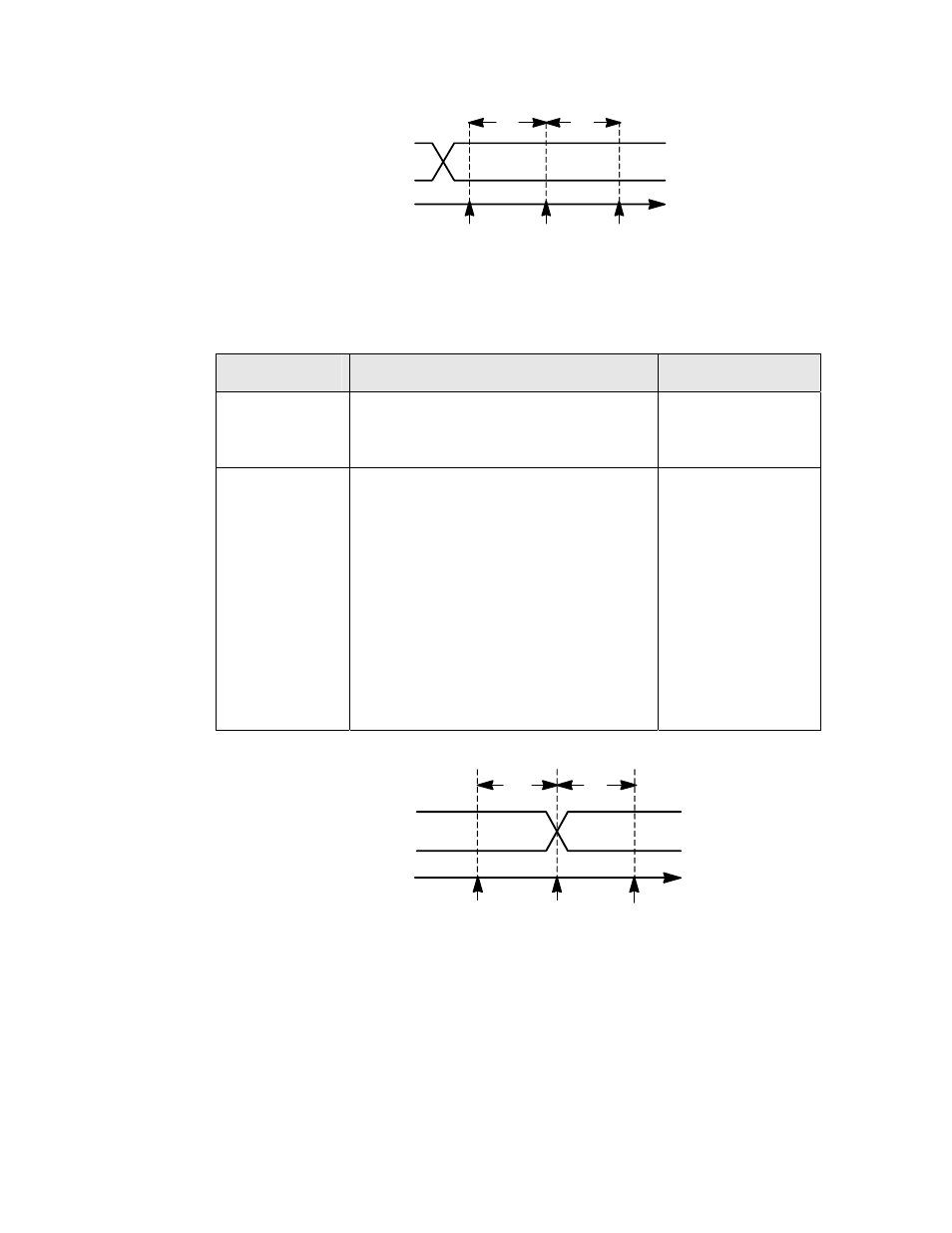

Figure 8. Bit Input Timing

Table 11. Bit Input Latency Values for Series 3100 Devices

Symbol

Description

Typical at 10 MHz

t

fin

Function call to sample

IO0 – IO10

IO11

41 μs

8.4 μs

t

ret

Return from function

IO0

IO1

IO2

IO3

IO4

IO5

IO6

IO7

IO8

IO9

IO10

IO11

19 μs

23.4 μs

27.9 μs

32.3 μs

36.7 μs

41.2 μs

45.6 μs

50 μs

19 μs

23.4 μs

27.9 μs

7.8 μs

OUTPUT PIN

UPDATED

END OF

io_out()

START OF

io_out()

TIME

OUTPUT

t

fout

t

ret

Figure 9. Bit Output Timing