Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 75

I/O Model Reference

65

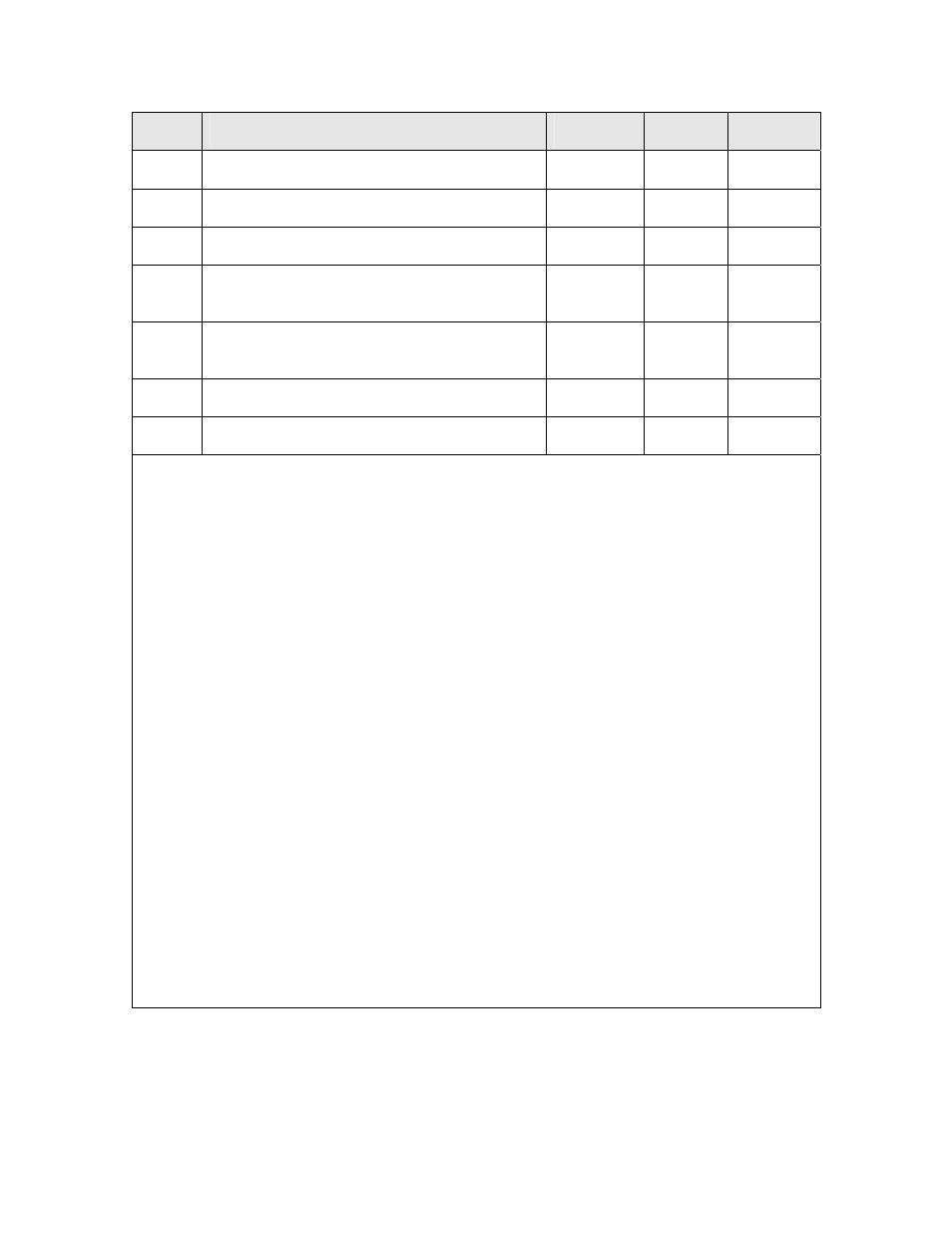

Symbol Description

Minimum

Typical

Maximum

t

sbas

A0 setup to falling edge of CS~

10 ns

—

—

t

sbah

A0 hold after rising edge of CS~

0 ns

—

—

t

sbwdv

CS~ to write data valid

—

—

50 ns

t

sbwdh

Write data hold after rising edge of CS~

(Notes 2, 3)

0 ns

30 ns

—

t

sbwdz

CS~ rising edge to Slave B release data bus

(Note 2)

— —

50

ns

t

sbrds

Read data setup before rising edge of CS~

25 ns

—

—

t

sbrdh

Read data setup before rising edge of CS~

10 ns

—

—

Notes:

1. The slave B write cycle (master read) CS~ pulse width is directly related to the slave

B write data valid parameter and master read setup parameter. To calculate the

write cycle CS~ duration needed for a special application use:

t

sbcspw

= t

sbwdv

+ master’s read data setup before rising edge of CS~.

Refer to the master’s specification data book for the master read setup parameter.

The slave read cycle minimum CS~ pulse width = 50 ns.

2. Refer to the appropriate Neuron Chip or Smart Transceiver data sheet for detailed

measurement information.

3. The data hold parameter, t

sbwdh

, is measured to the disable levels shown in the

appropriate Neuron Chip or Smart Transceiver data sheet, rather than to the

traditional data invalid levels.

4. In a slave B write cycle, the timing parameters are the same for a control register

(HS) write as for a data write.

5. Special applications: Both the state of CS~ and R/W~ determine a slave B write

cycle. If CS~ cannot be used for a data transfer, then toggling the R/W~ line can be

used with no changes to the hardware. That is, if CS~ is held low during a slave B

write cycle, a positive pulse (low to high to low) on R/W~ can execute a data transfer.

The low-to-high transition on R/W~ causes slave B to drive data with the same

timing parameters as t

sbwdv

(redefined R/W~ to write data valid). Likewise, the

falling edge of R/W~ causes slave B to release the data bus with the same timing

limits as the CS~ rising edge in t

sbwdz

. This scenario is only true for a slave B write

cycle, and is not applicable to a slave B read cycle or any slave A data transitions.

This application can be helpful if the master has separate read and write signals but

no CS~ signal. Caution must be taken to ensure the bus is free before transfers to

avoid bus contention.